# MBE growth and characterization of InAs based core-shell nanowire arrays

Master thesis

in

Materials science

Author: Doudou Wu February. 2021

submitted to

Faculty of Georesources and Materials Engineering

of the

RWTH Aachen University

Supervisor:

1. Prof. Dr. Regina Dittmann

RWTH

2. Prof. Dr. Detlev Grützmacher

Dr. Mihail Ion Lepsa

PGI-10

Forschungszentrum Jülich GmbH

### **Abstract**

Among III-V compound semiconductor nanowires, InAs nanowires have high electron mobility which make them suitable for low power field-effect transistors. The Fermi level pinning above its conduction band minimum results in easy fabrication of ohmic contacts. However, due to the large surface-to-volume ratio of nanowires, the surface states can have impact on the electrical property of InAs nanowires and therefore the influence of passivation is interesting to be investigated. The first part of this report focuses on the molecular beam epitaxy (MBE) growth of InAs nanowire arrays on prepatterned Si(111) substrates. Using a new in-situ Ga droplet assisted substrate preparation, a high reproducibility of the growth results with high nanowire yield is achieved. Afterwards, the in-situ passivation of InAs nanowire by Al<sub>2</sub>O<sub>3</sub> shell using atomic layer deposition (ALD) is successfully realized. In addition, the MBE growth of InAs-Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb core-shell nanowire is studied and the growth rate of AlGaSb shell is estimated. The second part is related to the fabrication of InAs nanowire-array based device using HSQ as planarization layer. After the fabrication, each nanowire array as a whole is connected by top and bottom electrodes vertically. The third part contains the DC electrical characterization of the InAs nanowire-array based devices at room temperature. The comparison between the resistivity of unpassivated and Al<sub>2</sub>O<sub>3</sub> passivated InAs nanowire arrays shows that the latter is lower demonstrating the benefit demonstrating the benefit of passivation.

# Table of content

| Abstract                                                                                 | 3  |

|------------------------------------------------------------------------------------------|----|

| Introduction                                                                             | 7  |

| 1. Theoretical and technical background                                                  | 9  |

| 1.1 Physical properties of InAs                                                          | 9  |

| 1.1.1 Crystal structure of InAs                                                          | 9  |

| 1.1.2 Surface properties of InAs                                                         | 9  |

| 1.2 Heterostructure of InAs/AlGaSb core/shell nanowires                                  | 11 |

| 1.3 Growth and characterization techniques                                               | 12 |

| 1.3.1 Molecular Beam Epitaxy                                                             | 12 |

| 1.3.2 Atomic layer deposition                                                            | 13 |

| 1.3.3 Scanning electron microscopy                                                       | 14 |

| 1.3.4 Ellipsometry                                                                       | 15 |

| 1.3.5. Atomic force microscope                                                           | 15 |

| 1.4 Metal-semiconductor contacts                                                         | 16 |

| 1.4.1 Schottky contact                                                                   | 16 |

| 1.4.2. Ohmic contact                                                                     | 17 |

| 2. Selective growth of InAs-based nanowire arrays by MBE                                 | 19 |

| 2.1 Selective growth of InAs nanowire – old method                                       | 19 |

| 2.1.1 Substrate preparation                                                              | 19 |

| 2.2 Selective growth of InAs/Al <sub>0.6</sub> Ga <sub>0.4</sub> Sb core-shell nanowires | 28 |

| 2.3 Selective growth of InAs nanowires by MBE – new method                               | 33 |

| 2.3.1 Growth mechanism                                                                   | 33 |

| 2.3.2 Growth results and analysis                                                        | 37 |

| 2.3.3 The influence of different substrate preparation processes                         | 38 |

| 2.3.4 The influence of different substrate re-oxidation before MBE growth                | 39 |

| 2.3.5 The influence of different hole diameters                                          | 39 |

| 2.3.6 The influence of growth time and different pitches                                 | 42 |

| 3. Passivation of InAs nanowire by ALD                                                   | 45 |

| 4. InAs nanowire-array based device fabrication                  | 47 |

|------------------------------------------------------------------|----|

| 4.1 Dicing                                                       | 48 |

| 4.2 Planarization with HSQ                                       | 49 |

| 4.3 Revealing the top of nanowires                               | 51 |

| 4.4 Top/bottom electrode fabrication                             | 54 |

| 4.4.1 First photolithography                                     | 55 |

| 4.4.2 Second photolithography                                    | 56 |

| 4.4.3 Metallization                                              | 59 |

| 4.5 Attempt to improve the quality of HSQ                        | 67 |

| 5. Electrical measurements and results                           | 70 |

| 5.1 Calculation of nanowire resistivity                          | 70 |

| 5.2 I-V characteristics of the InAs nanowire-array based devices | 71 |

| 5.3 Determination of the effective nanowire length               | 73 |

| 5.4 Resistivity results                                          | 75 |

| 6. Summary and outlook                                           | 77 |

| Bibliography                                                     | 79 |

| Acknowledgments                                                  | 82 |

# Introduction

Besides elemental semiconductor Si, III-V semiconductors which consist of elements from group III (AI, Ga, In) and from group V (N, P, As, Sb) are also of great importance for opto-electronic applications. In comparison with Si, III-V materials have some advantages: unlike Si which has indirect band gap, lots of III-V semiconductors exhibit direct band gap, for example GaAs, InP and InAs. III-V semiconductors with direct band gap enable direct recombination of electrons and holes which is suitable to build optoelectronic devices. For example, InP or GaAs based III-V semiconductor devices can be used for optical fiber communications, LEDs/LDs and solar cells [1]. In general III-V semiconductors have higher electron mobility than Si, especially the electron mobility of InAs is significantly high ( $\leq$ 40000 cm² V<sup>-1</sup> s<sup>-1</sup> [2]). Therefore it is a good candidate for high electron mobility and low power consuming devices [3]. Additionally, not only binary but also ternary and quaternary compounds can be formed and as a result heterostructures with desired band gap engineering are easy to realize by changing the material compositions.

Nowadays with the development of integrated circuits, it is intensively investigated the continuous decrease of the transistor dimensions, in order to increase device density, improve logic performance and to reduce the power consumption [4]. However, traditional Si based field-effect transistors are reaching their physical limits. One of the potential improvements is to use novel device architecture, e.g. switching from planar channel to a nanowire channel with a cylindrical gate-all-around (GAA) architecture [5]. By this method, the gate control is improved and the short-channel effects can be minimized, therefore enabling a shorter gate length.

Nanowires have attracted great attention because of their unique one-dimensional nanostructures. Among III-V compound semiconductor nanowires, InAs nanowire is a good candidate to be used as high mobility channel for field-effect transistors due to its high electron mobility.

The integration of III-V compound semiconductors on a Si chip provides new possibilities for the design and fabrication of electronic devices. However, the lattice mismatch between Si and compound semiconductors restrains the integration. One solution is the growth of nanowires (typical diameter no more than 100 nm) using selective area epitaxy, which means the localized epitaxial growth of nanowires on Si substrate through a

patterned amorphous dielectric mask, such as SiO<sub>2</sub> [6][7][8]. The nanowires can grow from the designed holes with nanometer-scale size, which enables the integration of compound semiconductors and Si regardless of the lattice mismatch and thermal coefficients. In this thesis, the electrical properties of InAs nanowires are measured vertically on the Si substrate, on which the nanowires growth takes place.

To obtain the electrical properties of InAs nanowires, they are usually measured singly and laterally. This method is time consuming and needs high requirements for the lithography. It is interesting to measure the I-V characteristic of InAs nanowires not singly but measuring many nanowires simultaneously. This can be realized by measuring a nanowire array vertically. This method can also avoid big deviations between measurement results of individual nanowires and an average resistance value of single nanowire can be finally obtained.

In this thesis, first, the MBE growth of InAs nanowire arrays on prepatterned Si(111) substrate is studied, with the goal to obtain high yield of vertical nanowires and high reproducibility. Then the In-situ passivation of InAs nanowire with Al<sub>2</sub>O<sub>3</sub> shell by ALD is studied. Afterwards, the InAs nanowire-array based devices are fabricated for two situations: InAs nanowires without any passivation and with Al<sub>2</sub>O<sub>3</sub> passivation. Finally, the electrical characterization for the two situations is performed. The influence of Al<sub>2</sub>O<sub>3</sub> passivation on InAs nanowire is discussed. Additionally, the growth of InAs/Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb core/shell nanowires by MBE is also presented.

# 1. Theoretical and technical background

# 1.1 Physical properties of InAs

InAs exhibits unique physical properties. It has narrow band gap (Eg=0.36eV at 300K), leading to low effective electron mass  $(0.023m_0)$  and high electron mobility ( $\leq 4x10^4$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) [9], which makes it a good candidate for field-effect transistors with high speed and low power consumption. InAs nanowires can be used as channels for nanowire field-effect transistors [10].

### 1.1.1 Crystal structure of InAs

Normally, the stable crystallographic structure of InAs bulk is zinc blende. Zinc blende structure can be seen as two face centered cubic lattices translated along the body diagonal by [1/4 1/4 1/4] a, where a is the lattice constant [11]. These two face centered cubic lattices are occupied by In and As respectively. The group III element In is at the position [0 0 0] while the group V element As is at the position [1/4 1/4 1/4]. The stacking sequence along [111] direction is ABCABC, according to the relative position of stacking layers. For nanowires, the stable crystal structure is a mixture of zinc blende and wurtzite [12][13]. The wurtzite structure has a hexagonal close packing structure with a basis of two types of atoms (In and As atoms). The stacking sequence is ABABAB along [0001] direction.

### 1.1.2 Surface properties of InAs

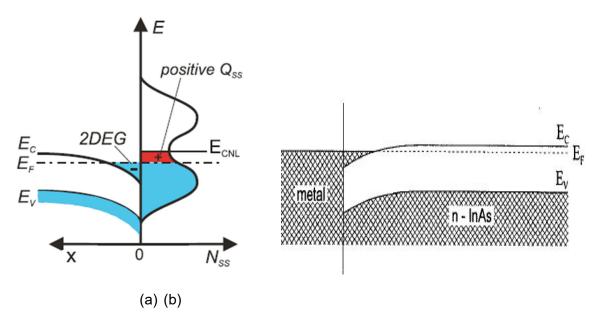

InAs has special surface properties. The surface atoms of semiconductor have less bonding partners, thus they do not have the same periodic structure as the bulk. Therefore, the energy structure of the surface is different from that of the bulk. When the surface density of states is extremely high, there is a surface Fermi level which is unchangeable and different from the bulk Fermi level, which is called Fermi level pinning. To achieve the thermodynamic equilibrium, the electrons move between surface and bulk. For InAs, the surface Fermi level pinning is above the conduction band minimum [14], thus the electrons transfer from the bulk to the surface. An electron accumulation layer is created at the surface so that a highly conductive 2-DEG (two dimensional electron gas) is formed at InAs surface. As a result, the intrinsic InAs is electrically conductive. The formation of the electron accumulation layer can be explained also by the Figure 1-1 (a), the electrons

are accumulated at the surface, because the charge neutrality level ( $E_{CNL}$ ) of the surface is located above the bulk Fermi level, so that electrons from the donor like surface states are transferred to the bulk living behind the positive surface charge ( $Q_{ss}$ ) to keep the charge neutrality [15]. The Fermi level pinning in the conduction band also leads to a metal-lnAs interface which is ideally to realize ohmic contact with low resistance [16], which means that no potential barrier exists between metal and semiconductor. The energy band diagram is shown in Figure 1-1 (b).

Figure 1-1 (a) The band structure of InAs at the surface. The x axis refers to the distance to the surface and the  $N_{ss}$  axis refers to the surface state density per energy. Taken from [17]. (b) The band structure of metal-InAs contact.

As mentioned before, the surface states of InAs is an important factor to influence the transport properties. Compared with InAs bulk system, InAs nanowire has larger surface-to-volume ratio, so that the effect of the surface states on the transport properties of InAs nanowires can be significant [18]. They can result in a stronger ionized impurity scattering than bulk material. In addition, there is a strong surface roughness scattering. These factors can lead to a smaller electron mobility in the surface region [19]. Therefore, it is interesting to investigate the influence of surface passivation. In air atmosphere, a native oxide layer is created on InAs nanowire surface, which is however not a stable passivation layer. High k dielectrics such as Al<sub>2</sub>O<sub>3</sub> can act as gate oxides or as a passivation of the nanowire surface. It is expected that with the in-situ Al<sub>2</sub>O<sub>3</sub> passivation, the surface scattering can be reduced and the transport properties of InAs nanowire can be enhanced.

### 1.2 Heterostructure of InAs/AlGaSb core/shell nanowires

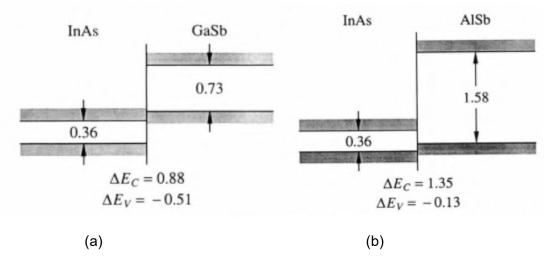

Growing radial nanowire heterostructures can create unique interface properties. There are three of types of III-V semiconductor heterojunctions, type I: straddling alignment, type II: staggered alignment and type III: broken-gap alignment. The experimentally determined band alignments for InAs/GaSb and InAs/AISb are shown in Figure 1-2. The band alignment of InAs/AI<sub>x</sub>Ga<sub>1-x</sub>Sb can have a staggered or broken gap band alignment, which is dependent on AI content.

Figure 1-2 (a) InAs/GaSb interface exhibits broken-gap alignment, (b) InAs/AlSb interface exhibits straddling alignment [20].

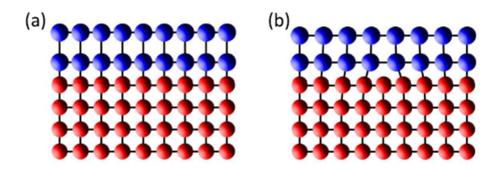

Because different materials have different lattice constants, the interface of heterostructure is normally lattice mismatched. Below critical thickness of shell, pseudomorphic growth is possible, while the structure is relaxed by the formation of dislocation beyond critical thickness, as shown in Figure 1-3. Therefore, it is necessary to know the critical thickness of researched structure. For core/shell nanowire, the critical thickness of the shell is dependent on the lattice mismatch degree of the material combination and the core radius. For InAs/AlGaSb, the lattice mismatch degree is very low (between 0.6%-1.2%). For planar structure, the critical thickness for GaSb is 20nm and for AlSb is 10nm according to the classical Matthews-Blakeslee theory [21]. But for InAs/AlSb as well as InAs/GaSb core-shell nanowires, the critical thickness with misfit-dislocation-free shell growth is at least twice as thick as for the planar structure, as discussed in [22]. For InAs/AlGaSb core-shell nanowires, dislocation-free shell thickness is expected to be larger than 20nm.

Figure 1-3 (a) Pseudomorphic growth and strained lattice structure (b) Dislocation formation and relaxed lattice structure. Taken from[23].

# 1.3 Growth and characterization techniques

### 1.3.1 Molecular Beam Epitaxy

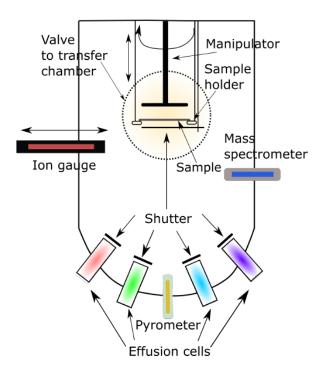

Molecular Beam Epitaxy (MBE) is used in this thesis to grow InAs nanowires and InAs/AlGaSb core/shell nanowires. MBE is one of the fundamental tools to grow epitaxial semiconducting materials. The schematic is shown in Figure 1-4. The elemental materials are heated separately in effusion cells to a temperature where the elements can evaporate or sublimate. MBE requires ultra-high vacuum (typically  $10^{-10}$  mbar), this extremely low chamber pressure ensures the purity of deposited materials and also ensures a long mean free path of evaporated atoms. The evaporated atoms therefore will not react with each other in chamber but only on the substrate. The fluxes of materials, which determine the deposition rate to a great extent, are controlled by cell temperatures. The group V materials As and Sb are stored in the reservoirs of valved cracker sources. The fluxes can be adjusted by valve position and reservoir temperature. Arsenic is supplied mainly as As<sub>4</sub> or As<sub>2</sub> depending on the cracker temperature. When the cracker temperature is  $600^{\circ}$ C, arsenic evaporates from cell as As<sub>4</sub>, while arsenic evaporates from cell as As<sub>2</sub>, when the cracker temperature is  $900^{\circ}$ C. In this report, the cracker temperature is set at  $600^{\circ}$ C.

Figure 1-4 Schematic of the principal parts of a typical molecular beam epitaxy reactor (MBE). Taken from [24].

The fluxes of elements are proportional to the beam equivalent pressures (BEPs), which are measured with ionization gauge All the cell temperatures can be regulated by a software program.

### 1.3.2 Atomic layer deposition

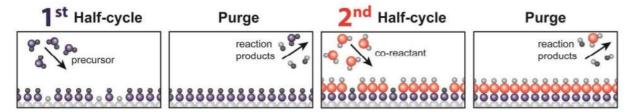

Atomic layer deposition (ALD) is a vapor-phase deposition technique which can be used to grow high-quality thin film, e. g. high κ films such as Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>. The ALD technology is based on a sequential, self-limiting surface chemistry. During the growth, the precursor and co-reactant are offered into reactor alternatively. As shown in Figure 1-5, precursor A is added into the reactor first and one layer of precursor A is deposited on the substrate surface. Then the reactor is purged in order to get rid of all residual precursor from the reactor. Afterwards, the co-reactant B is inserted to react with the layer of precursor A. The reaction happens at the sample surface in a self- limited way. Finally, the chamber is purged again. These four steps constitute an ALD cycle. After one cycle, one atomic layer of required material is generated. The thickness of material depends on the number of cycles. The thickness can be precisely controlled at the sub-nanometer

level by varying the cycle numbers. The ALD process happens at relatively low temperature with high uniformity and conformality [25]. These benefits make ALD an attractive method for semiconductor applications.

In this thesis, to deposit  $Al_2O_3$  layer by ALD, precursor A represents trimethylaluminum (TMA,  $Al(CH_3)_3$ ) and co-reactant B represents  $H_2O$ .

Figure 1-5. Schematic of an ALD cycles. The first half-cycle describes the deposition of precursor and the second half-cycle describes the deposition of co-reactant, with a purge process in between. The exposure time need to be sufficient to get saturated growth, and the purging time also need to be sufficient to avoid the reaction of the precursor and co-reactant directly in the gas phase. Adapted from [25].

### 1.3.3 Scanning electron microscopy

Scanning electron microscopy (SEM) is the most used characterization technique in this study to inspect the morphology of grown nanowires and fabricated devices. In high vacuum conditions, a focused electron beam scans the specimen surface. The electrons interact with the atoms of the specimen and produce various kinds of signals including secondary electrons (SE), back-scattered electrons (BSE), characteristic X-rays etc. Topography information can be obtained by the SE mode. In this mode, low-energy electron beam interacts with sample inelastically and secondary electrons are excited from surface or near surface regions. The information of secondary electrons are detected by secondary electron detector. In the SE mode, topographical image with resolution less than 0.5nm is possible to obtain. Additionally, for conventional SEM imaging, specimens need to be electrically conductive, because nonconductive specimens will collect charges during electron beam scanning and it will be difficult to obtain accurate surface topography images.

### 1.3.4 Ellipsometry

Spectroscopic ellipsometry is used to determine the optical constants and the thickness of thin films. In this study, the thickness of thermal SiO<sub>2</sub>, PMMA, HSQ, AZ5214E and Al<sub>2</sub>O<sub>3</sub> deposited by ALD are all obtained using the ellipsometer.

During measurements, the incident beam interacts with material structure (e. g. reflection, absorption, scattering and transmission can happen), the polarization of light will be changed afterwards due to different optical properties of material and different film thickness. The change of polarization is parameterized by the amplitude ratio  $\psi$  and the phase change difference  $\Delta$ . Afterwards, a data analysis must be performed using the correct layer optical model and layer sequence. As a result, the thickness of layers can be calculated.

### 1.3.5. Atomic force microscope

Atomic force microscope (AFM) technology is based on the atomic force between tip and sample to explore the topographic information of the sample surface in the nanoscale range. A sharp tip is mounted at the free end of the cantilever. During scanning, the position detector records the deflection of the cantilever through a laser beam reflection change. There are three traditional modes of AFM: contact mode, non-contact mode and tapping mode. In contact mode, the tip of AFM is touching the surface during measuring and the deflection changing of the cantilever is the feedback value. In non-contact mode, the tip and the sample are not in contact each other, the cantilever always oscillates at resonance. In tapping mode, the tip and the sample have an intermittent and short contact during scanning, the cantilever oscillates at a fixed driving frequency which is at or very close to the free resonance frequency. The change of amplitude is dependent on the tipsample distance monotonously. The amplitude change is set as feedback signal in this method. The disadvantage is that the force between tip and sample is hard to control. which could lead to damage of the sample. Another mode---peak force tapping mode, which was launched by Brucker in 2010 is superior. In this mode, the tip-sample distance is modulated in a sinusoidal motion, which means the closer the probe to the sample surface, the slower is the motion of the probe relative to the sample surface. This feature ensures the accurate control of the tip-force interaction. The tip-sample interaction is controlled by maintaining the peak force (pN-level) between tip and sample constant The peak force is measured by the deflection of the cantilever. This method provides highresolution imaging and protects the sample and as well as the tip from damage. In this

study, the depth of the holes on prepatterned SiO<sub>2</sub>/Si substrate is determined by AFM using peak force tapping mode.

### 1.4 Metal-semiconductor contacts

In this thesis, in order to measure the I-V characteristic of InAs nanowire arrays, metal-semiconductor contacts are fabricated. Therefore, it is of importance to understand metal-semiconductor contacts and their influences on I-V characteristics of nanowires. Basically, there are two kinds of metal-semiconductor contacts: Schottky contact and ohmic contact.

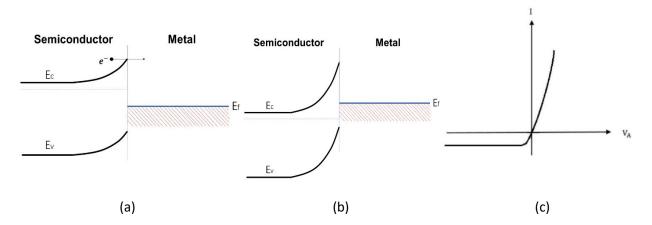

### 1.4.1 Schottky contact

When metal and semiconductor get into contact, the energy band diagram of the metal and the semiconductor are aligned using the same vacuum level, and the Fermi levels of the two materials are misaligned due to different work functions. Then, the charge carriers will move from one material to the other until they reach the thermal equilibrium. For example, for an n-type semiconductor, if its work function  $\Phi_m$  is smaller than that of the work function of the metal  $\Phi_s$ , as shown in Figure 1-6, the electrons will flow from semiconductor to metal until reaching the thermal equilibrium, which will result in a depletion layer at the interface of the semiconductor side. Accordingly, the energy band structure is bent upwards and a potential energy barrier is built at the interface. This kind of contact is named Schottky contact. The barrier height  $\Phi_B$  is the difference between metal work function  $\Phi_m$  and the electron affinity  $\chi$  of the semiconductor. The electron affinity  $\chi$  and the metal work function  $\Phi_m$  are invariant values depending only on the materials which will not change during contacting.

Figure 1-6 (a) Energy band diagram of a metal adjacent to n-type semiconductor under thermal non-equilibrium condition. (b) metal-semiconductor contact in thermal equilibrium. Taken from [26]

Such a Schottky contact has rectifying property: under forward bias (V>0, a positive voltage V is applied on the metal and the semiconductor is connected to the ground.), the Fermi energy of the metal becomes lower than the Fermi energy in the semiconductor, the potential barrier from the semiconductor side is lower, which means that it is easier for electrons in the semiconductor to flow into the metal. As a result a large current is achieved. While under reverse bias (V<0, a negative voltage V is applied on the metal and the semiconductor is connected to the ground.), potential barrier becomes larger, the diffusion of electrons from semiconductor to the metal will be blocked. Only a small amount of thermally excited electrons in the metal is able to overcome the potential barrier and the corresponding current is very small. At very high reverse biases, the depletion region breaks down and the current becomes extremely large. The changed energy band structure is shown in Figure 1-7 (a) and (b). In general, the relationship between current flowing through the Schottky contact and the applied voltage can be described as:

$$I=I_0 (e^{qV/kT}-1)$$

(1.1)

Where I<sub>0</sub> is the saturation current, V is the applied voltage, q is the electronic charge, T the absolute temperature and k the Boltzmann constant. The typical I-V characteristic of a Schottky contact is shown in Figure 1-7 (c).

Figure 1-7 (a) The band structure at Schottky contact interface under forward bias. (b) The band structure at Schottky contact interface under reverse bias. (c) I-V characteristics of a Schottky contact.

### 1.4.2. Ohmic contact

In order to gain the electrical properties of InAs nanowires, the metal-semiconductor contact resistance should be minimized, and Ohmic contacts should be realized. An ideal Ohmic junction has low resistance and non-rectifying property which means no potential

barrier exists between the metal-semiconductor interface. The transformation of Schottky contact into ohmic contact can be realized by lowering the potential barrier or making the barrier very narrow by doping it heavily.

In this thesis, the Ti/Au-InAs top contact is ohmic because the Fermi level pinning of InAs results in a negative potential barrier and there is an electron accumulation layer at the InAs surface. Therefore, the electrons in InAs and metal can flow into each other without barrier, as clarified in section 1.2.2. The Ti/Au-silicon bottom contact is also ohmic because the silicon substrate is heavily n-doped, thus, the potential barrier is very thin and electrons can tunnel through the thin barrier.

# 2. Selective growth of InAs-based nanowire arrays by MBE

### 2.1 Selective growth of InAs nanowire – old method

### 2.1.1 Substrate preparation

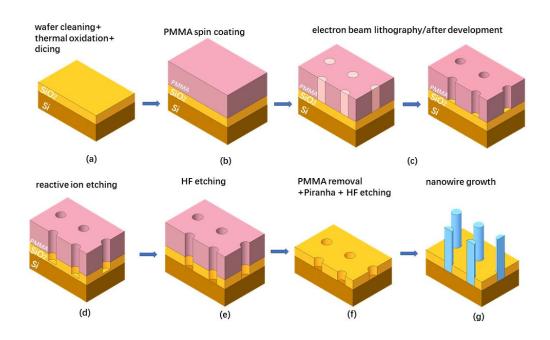

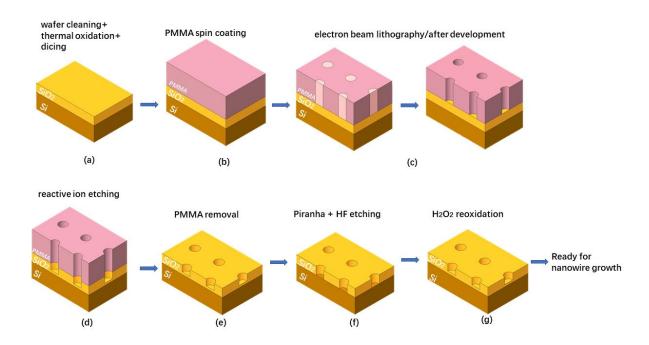

An appropriate substrate preparation is essential to obtain high yield of vertical InAs nanowires-. First, the substrate preparation process from [27] and [28] was followed and is modified afterwards. The detailed process is illustrated in Figure 2-1 and is described as following:

- a) The 4 inch n-doped Si (111) wafers are wet chemically cleaned in Piranha solution (96% H<sub>2</sub>SO<sub>4</sub>: 37% H<sub>2</sub>O<sub>2</sub> = 3:1 in volume) for 10min to get rid of organic contaminants and rinsed in DI water also for 10 min. Then, the wafers are cleaned with 1%HF solution for 10mins to remove native oxide. After each step, they are dipped into DI water for 10min. The wafers are transferred afterwards into the oxidation furnace for the growth of 20nm thermal oxide. The thickness of silicon dioxide is measured by ellipsometry in general obtaining the desired value, 20±1 nm. To protect the surface during dicing, the wafers are spin-coated with resist AZ5214E at 6000rpm (acc. 4000rpm) for 30s and then soft bake at 90°C for 5min. Afterwards the wafers are diced into 2.5x2.5cm<sup>2</sup> samples. The AZ5214E resist is then cleaned with ultrasonic bath with acetone for 10min and isopropanol for 5min. The schematic of the substrate after this step is shown in Figure 2-1 (a).

- b) Afterwards, the samples are spin-coated with resist PMMA 950K 679.04 at 6000rpm for 60s and baked at 180°C for 10min, as shown in Figure 2-1 (b). In order to enhance the adhesion between PMMA and Si/SiO<sub>2</sub> substrate, a priming process using hexamethyldisilizane (HMDS) at 130°C is performed prior to PMMA spin coating. The thickness of PMMA is 220nm±10nm after baking: This can vary with PMMA storage time, long storage time leads to higher PMMA thickness due to less solvent inside.

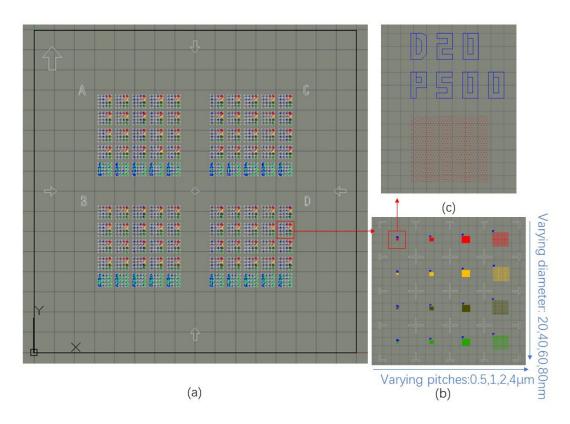

- c) Then, the samples are sent to do the electron beam lithography (see Figure 2-1 (c)) using the writing pattern and expose doses from [28], as shown in Figure 2-2 and Table 2-1. Next, the samples are dipped into AR-60055 for development for 70s and transferred into isopropanol for 3min to stop the development.

- d) To remove possible residual resist in the pattern holes, 15s oxygen plasma cleaning (300W, 200sccm) at Giga batch is used. Afterwards the samples are transferred to the reactive ion etching (RIE) chamber. The gas CHF<sub>3</sub> (50sccm) is used in RIE process at working temperature 20°C. Because the thickness of SiO<sub>2</sub> is ~ 20 nm, the etching depth need to be larger than 15nm but smaller than 20nm in order not to damage the Si surface (see Figure 2-1(d)). The RIE time determination will be discussed in session 2.1.3.

- e) The left SiO<sub>2</sub> inside the holes is finally removed by using an 1% HF solution (see Figure 2-1(e)).

- f) The PMMA resist is removed by acetone (6min) and isopropanol (2min) using ultrasonic bath. 10min oxygen plasma cleaning (300W, 200sccm) at Giga batch is used afterwards to ensure a resist-free surface. The samples are cleaned again 10min in Piranha solution) and rinsed in DI water for 10min. To remove the oxide resulted during Piranha cleaning, the samples are dipped 1 min into 1% HF solution exposing the bare silicon surface inside the holes (see Figure 2-1(f)).

- g) The samples have to be loaded into the load lock chamber of the MBE system within 30min to avoid re-oxidation of Si surface. In the load-lock chamber the samples are baked at 200°C for 45min. Then, they are transferred into the preparation chamber and baked at 700°C for 1h. Now, they are ready for nanowire growth in the MBE chamber.

Figure 2-1. Schematic of the substrate preparation process.

Table 2-1 Electron beam dose used for different hole diameters.

| Hole diameter (nm) | Exposure dose         |

|--------------------|-----------------------|

|                    | (µC/cm <sup>2</sup> ) |

| 20                 | 1344                  |

| 40                 | 544                   |

| 60                 | 410                   |

| 80                 | 350                   |

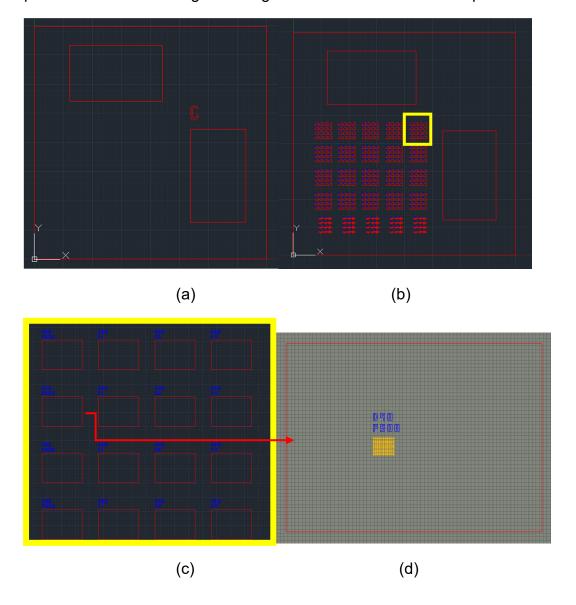

Figure 2-2. AutoCAD electron beam lithography mask from[28] (a) the whole pattern on the  $2.5x2.5cm^2$  sample. There are four identical parts, A, B, C and D, and each part consists of 4x5 square areas with hole arrays. The last row of each part contains special patterns which is not used in this thesis; the other four rows have identical square areas. (b) close-up of one of the square areas, which contains 4x4 nanowire arrays with pitches (distance between holes)  $0.5 \mu m$ ,  $1 \mu m$ ,  $2 \mu m$ ,  $4 \mu m$  and hole diameter 20nm, 40nm, 60nm, 80nm. (c) close-up of one of the nanowire arrays: D20P500 (D: diameter, P: pitch), the red points are the holes. There are totally 900 holes (30\*30) in one nanowire array.

### 2.1.2 Growth mechanism of InAs nanowires

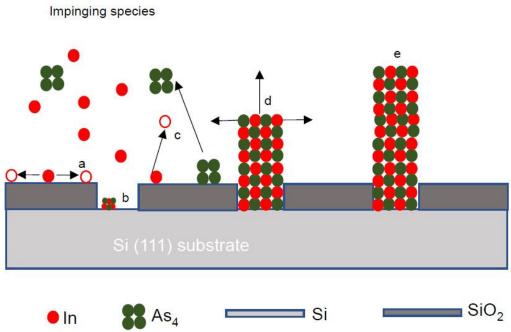

Two growth methods without any foreign catalyst, e. g. Au, have been investigated before: (a) vapor-liquid-solid (VLS) mechanism, in which the group III element acting as selfcatalyst [29] and (b) vapor-solid (VS) growth mechanism which does not require any catalyst but the nanowires are self-seeded [30]. The second method is adopted in this thesis. The mechanism is shown schematically in Figure 2-3. The In atoms and As4 molecules are evaporated from effusion/cracker cells and impinge on the substrate surface. The prepatterned holes, in which bare Si surface is exposed, are suitable to serve as nucleation sites since the sticking coefficient of In adatoms on Si(111) is much higher than on SiO<sub>2</sub> [31]. Then, the growth is continued by absorbing adatoms which diffuse along the surface or through direct incorporation of the impinging species. This results in the radial and axial growth of the nuclei and they finally turn into InAs nanowires. Besides the material fluxes, the substrate temperature is also important to determine the nanowire growth rate. At high temperatures, decreased nanowire length is observed due to increased thermally activated In adatom desorption and increased thermal decomposition of InAs [6][31][32]. On the other hand, at low temperature, the nanowire length is also inhibited due to the reduced diffusion length of In adatoms and therefore higher sticking coefficient, so that the incorporation rate contributing to nanowire growth is also lower. For InAs nanowire, as discussed in [6], the optimal growth temperature window is 480-510°C. In this thesis, 480°C and 460°C are used, with which good results can obtain. The substrate temperature is measured by a thermocouple and accurately controlled by dedicated controllers. The controller parameters and temperature can be set remotely using a computer software.

Figure 2-3. Schematic of InAs nanowire growth. (a) Surface diffusion of In atoms, for confining into holes (b) Formation of critical nuclei (c) Desorption of In and As from the oxide surface (d) Nanowire starts to grow in the radial and axial directions (e) Nanowire growth. Taken from [28]

The MBE growth recipe is as followed: First, the substrate temperature is set at 480°C with As beam equivalent pressure (BEP) of 4 × 10<sup>-5</sup> mbar for 10min. Then, the In shutter is opened, the flux corresponding to a growth rate of 0.08 μm/h (determined by the growth rate of a planar InAs layer). the As BEP remains at 4 × 10<sup>-5</sup> mbar and the nanowire growth starts. After 10 min growth, the substrate temperature is reduced to 460°C in 5 min. Simultaneously the In rate is reduced to 0.03 μm/h and As BEP is reduced to 2.5 × 10<sup>-5</sup> mbar. This growth conditions are maintained until the end of the growth and the corresponding time is defined as the growth time and determines the nanowire length. In this recipe, the higher In rate and As flux at the beginning aim to facilitate nucleation and the lower In rate and As flux afterwards aim to restrain the lateral growth of nanowires [27].

### 2.1.3 Problems regarding to growth results

To investigate the influence of different RIE etching time on nanowire growth, two substrates are fabricated with RIE time 110s and 150s respectively. 150s is the previous parameter used in our institute to etch 15nm SiO<sub>2</sub> inside the holes. 110s is newly estimated, which is the time needed to etch 15nm SiO<sub>2</sub> inside the holes, under the

estimation that the etching rate inside holes is 60% of the etching rate on a planar SiO<sub>2</sub> layer (planar etching rate: 0.23±0.025nm/s). The growth results are shown in Figure 2-3.

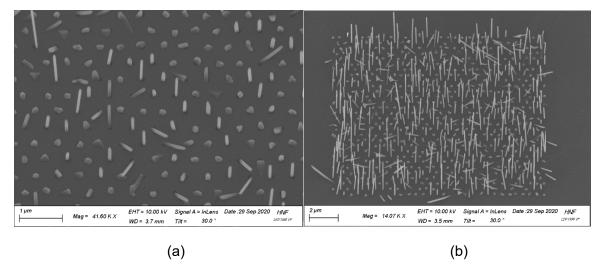

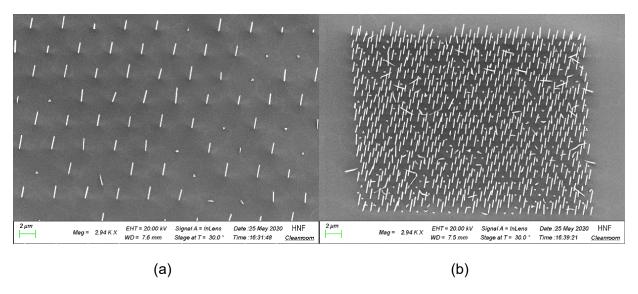

Figure 2-4. (a) Nanowire growth with RIE time 110s and growth time 3h (region D80P500) (b) Nanowire growth with RIE time 150s and growth time 2h30min (region D60P500).

By comparing the SEM images of the two samples, it can be seen that the RIE time 110s might be not enough. As seen in Figure 2-3 (a), the yield of vertical nanowires is less than 30% and there is a large amount of crystallites. The formation of crystallites instead of nanowires might be due to residual silicon dioxide in the bottom of the holes, so that the axially epitaxial growth can hardly accomplish resulting in crystallite growth, or can only accomplish very late, which leads to the formation of short nanowires (most of them are not longer than 500nm). In comparison, on the sample with RIE time 150s, long nanowires have grown even though the growth time is with 30min shorter than for the other sample, which at least means that the RIE time is more suitable, the nucleation occurs easier and InAs nanowires start to grow earlier. However, the yield of vertical nanowires is not more than 50%, and there are many tilted nanowires and crystallites, which is not suitable for nanowire-array based device fabrication. Another problem for both samples is that there are some empty holes after the growth for hole diameters of 20, 40, 60 nm, which afterwards is proved that it is due to much lower In flux than desired value, rather than insufficient electron beam doses. Insufficient In flux results in less nucleation probability and therefore, there are many empty holes.

Two approaches are used to improve the yield of vertical nanowires. The first approach is to modify the RIE time. Insufficient RIE time leads to problems with nucleation, but too long RIE time can damage Si surface which might also lead to crystallite growth.

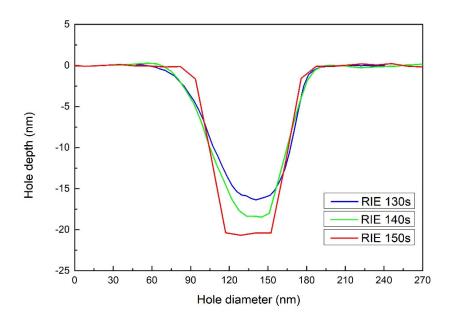

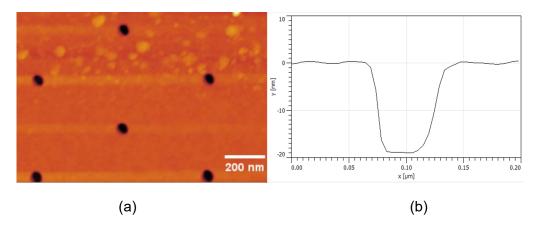

Therefore, it is important to find out a suitable RIE time. To clarify the hole depth after RIE, 3 samples were processed with RIE time 130s, 140s, 150s respectively. After RIE process, the hole morphology is measured with AFM. The hole profiles are shown in Figure 2-5. The average hole depth is shown in table 2-2. 150s RIE etching time gives a hole depth slightly higher than 20nm, which means there is almost no SiO<sub>2</sub> left inside the holes, the silicon surface is probably damaged, which could be the reason why the sample with RIE time 150s presented in section 2.1.3 has low vertical nanowire yield. The RIE etching time of 130s was considered in the subsequent experiments. An average hole depth of 17.25nm in average and is supposed to provide an undamaged silicon surface.

Figure 2-5. The hole morphology after different RIE times under AFM measurement.

Table 2-2

| RIE time/s | Hole depth in average/nm |

|------------|--------------------------|

| 130        | 17.25±0.33               |

| 140        | 18.47±0.39               |

| 150        | 20.30±0.21               |

The second approach is related to the re-calibration of the In flux (growth rate). Much lower In flux than desired in the growth experiments presented at the beginning of this section is due to an incorrect correspondence between the In effusion cell temperature and In deposition rate. A correct calibration of the In growth rate is the precondition to get

reliable growth results. RHEED (Reflection high-energy electron diffraction) is used to make the calibration.

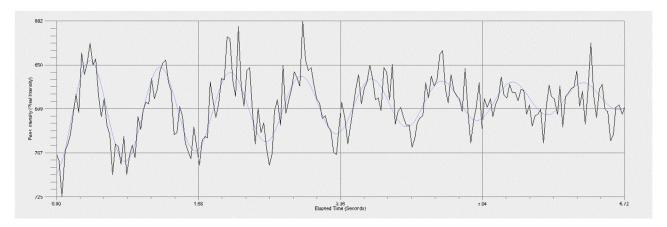

The experiment for In growth rate calibration was carried out on a GaAs substrate. The substrate temperature was set at  $550^{\circ}$ C. In<sub>x</sub>Ga<sub>1-x</sub>As was grown on a GaAs substrate. Growth rates ( $\mu$ m/h) are measured by the oscillation of RHEED intensity. the image of a RHEED intensity oscillation is shown in Figure 2-6, the intensity of the curve represents the surface coverage of the growing thin film. Each peak corresponds to a new monolayer formation, the layer growth rate can be obtained by measuring the oscillation frequency.

The growth rate of GaAs is kept at  $1\mu$ m/h, the growth rate of  $In_xGa_{1-x}As$  is changed in the range of 1.05-1.2  $\mu$ m/h. With stepwise changing the In cell temperature, the growth rate of  $In_xGa_{1-x}As$  is measured by the intensity oscillations of RHEED specular spot. Accordingly, the growth rate of  $In_xGa_{1-x}As$  is 1.20  $\mu$ m/h, so that the growth rate of  $In_xGa_{1-x}As$  is 1.20  $\mu$ m/h, so that the growth rate of  $In_xGa_{1-x}As$  is 1.20  $\mu$ m/h, so that the growth rate of  $In_xGa_{1-x}As$  is 1.20  $\mu$ m/h, so that the growth rate of  $In_xGa_{1-x}As$  is 1.20  $\mu$ m/h, so that the growth rate of  $In_xGa_{1-x}As$  is 1.20  $\mu$ m/h, so that the growth rate of  $In_xGa_{1-x}As$  is 1.20  $\mu$ m/h, so that the growth rate of  $In_xGa_{1-x}As$  is 1.20  $\mu$ m/h, in cell temperature is obtained. For example, to use an  $In_xGa_{1-x}As$  in  $In_xGa_{1-x}As$  is 1.20  $In_xGa_{1$

Figure 2-6. RHEED intensity oscillations during growth of  $In_xGa_{1-x}As$ . The x axis shows the elapsed time and y axis shows the intensity of the measured specular spot. To get this graph, In cell was set at 930°C. The growth rate of  $In_xGa_{1-x}As$  is 1.20ML/s, which is equivalent to 1.20µm/h.

After modifying the In growth rate calibration and RIE time, the growth results have shown a higher yield of vertical nanowires, as shown in Figure 2-7. The yield of vertical nanowires can be up to 80%.

Figure 2-7. SEM micrographs of a sample with RIE time 130s and new In growth rate calibration. (a) Nanowires from region D80p4 (b) nanowires from region D40P1. The growth time is 2h30min.

However, even this optimized growth method does not show high reproducibility. With the same substrate preparation parameters, the growth results are not identical from batch to batch. The reason could be that the etching rate in the RIE equipment is not stable, or that the properties of SiO<sub>2</sub> vary from batch to batch. One proof is that the depth of the holes after a RIE time of 110s measured two months later, is 18.75nm (evaluated from 6 holes), as shown in Figure 2-8. is almost equal to the etching depth for RIE time 140s which was measured before in Figure 2-5.

Figure 2-8. AFM measurements after 110s RIE time (details in text). (a) AFM image from region D80P500 (b) cross-sectional profile of one of the holes.

### 2.2 Selective growth of InAs/Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb core-shell nanowires

In this section, the growth, morphological and structural analyses of InAs/Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb core-shell nanowire arrays are presented. InAs/Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb core-shell nanowire heterostructure is supposed to have a staggered band alignment [33]. This structure in combination with a superconductor shell can be used for the study of the coupling of semiconductor-based quantum dot qubits.

The substrate fabrication process is the same as in section 2.1.1. In the growth process by MBE, after the growth of InAs nanowire array following the recipe described above, the In and As fluxes are stopped and the substrate temperature is reduced from  $460^{\circ}$ C to  $330^{\circ}$ C in 10min. During this time, the Sb shutter is opened and kept like this till the end of the growth. the Sb BEP is set to  $1.5 \times 10^{-6}$  mbar. After another 2min to stabilized the substrate temperature, the Ga and Al shutters are opened, the growth rates being set at  $0.04\mu\text{m/h}$  and  $0.06\mu\text{m/h}$ , respectively. After the growth of the  $Al_{0.6}Ga_{0.4}Sb$  shell for a certain time, the Al shutter is closed and the Ga growth rate is set to  $0.1\mu\text{m/h}$  for the growth of GaSb for 15min. According to [23], the GaSb shell growth rate is around 23nm/h, As a result, the thickness of the thin GaSb layer after 15min growth is supposed to be around 5.75nm. The thin GaSb shell prevent the fast oxidation of the  $Al_{0.6}Ga_{0.4}Sb$  shell., otherwise an oxide layer of 8-10nm can be formed,, as mentioned in [22].

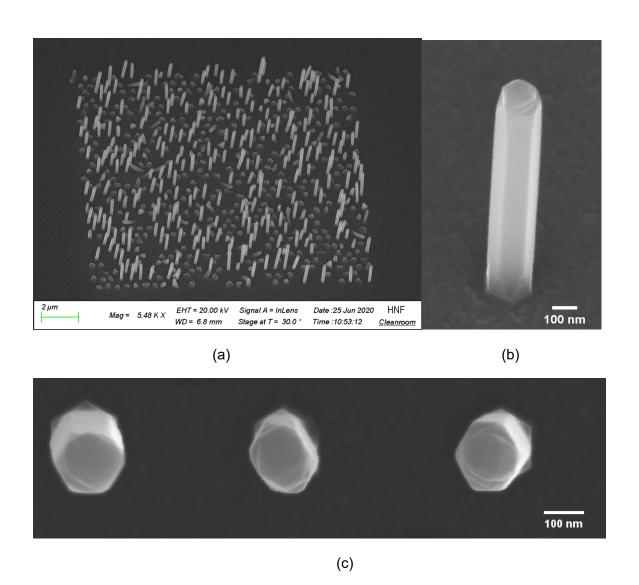

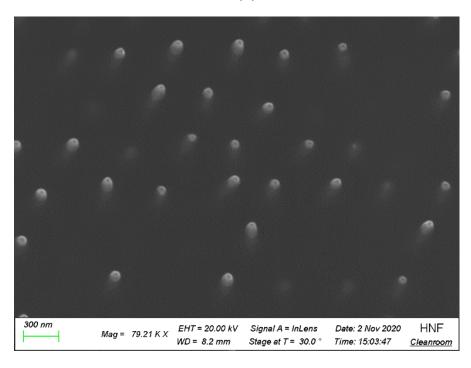

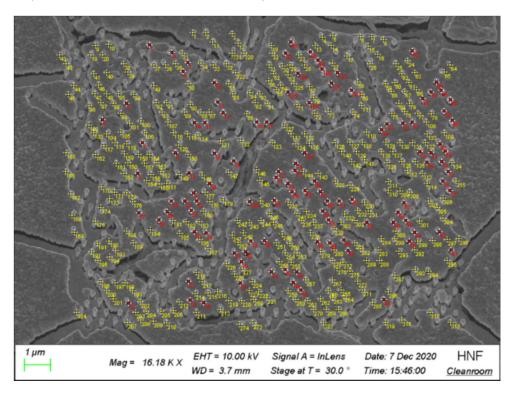

In order to obtain the Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb shell growth rate, shells are grown for 15min, 30min and 45min. The growth results with an AlGaSb shell growth time of 45min is shown in Figure 2-9. The growth time of the InAs core is 2h30min corresponding to a nanowire length and diameter of 2-3µm and 150-180nm, respectively. The Figures 2-9 (b) and (c) show that InAs/Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb core-shell nanowires have hexagonal morphology.

Figure 2-9. SEM micrographs of  $InAs/Al_{0.6}Ga_{0.4}Sb$  core-shell nanowires with the core and shell growth time of 2h30min and 45min, respectively. (a) The 30° tilted SEM image of the array D40P500. (b) Close-up of one single nanowire (also 30° tilted SEM image). (c) Top view image of the nanowires. The nanowires with shell growth time of 30min and 15min have similar morphology except a smaller diameter.

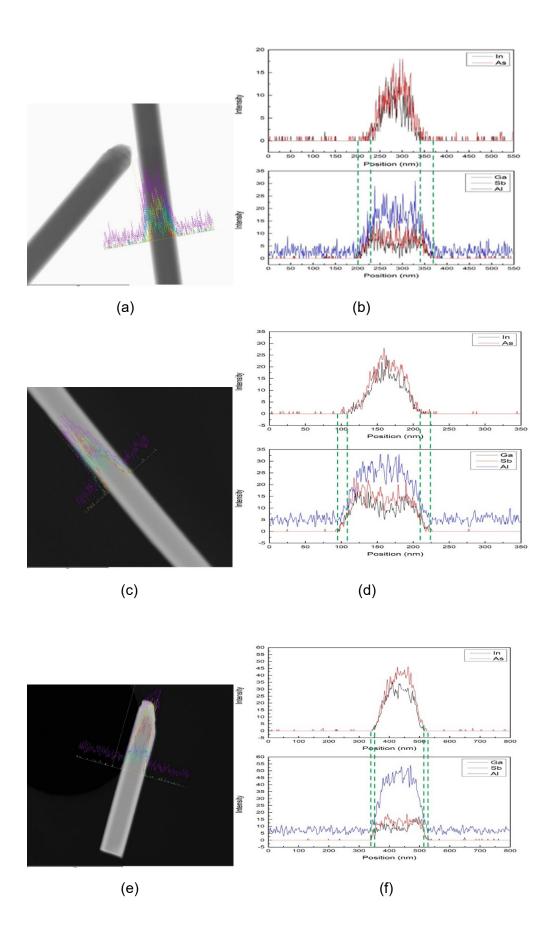

Figure 2-10. The EDX measurement of InAs/Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb core-shell nanowires with shell growth times 45min (a) and (b) , 30min (c) and (d) and 15min (e) and (f). (a)(c) and (e) show the nanowire morphology and scan lines and (b)(d)(f) show the corresponding relationship between the elemental intensity and scan position. In the lower images in (b)(d) and (f), the blue line represents Al, red line Sb and black line Ga.

In order to get the elemental distribution inside the nanowires, energy dispersive X-ray (EDX) analysis is performed. EDX is an elemental characterization method. Due to the fact that each element has a unique atomic structure, the peak on the X-ray emission spectrum is also unique and elemental information can be obtained. For measurements, the nanowires are transferred mechanically from the substrate to copper TEM grids with holey carbon films. Then, the middle part of the nanowires is scanned transversally by EDX. The results are shown in Figure 2-10. For each sample, the EDX signals of In/As and Al/Ga/Sb are shown in upper and lower images in (b)(d) and (f) respectively. The signals of In and As appear at the same position range, the signals of Al, Ga and Sb appear at a larger range than In and As, which indicate the presence of an AlGaSb shell. The intensity of In and As signal has a maximal value at the center of the core while the intensity of Al, Ga and Sb signal has a slightly decrease along the core of the nanowires.

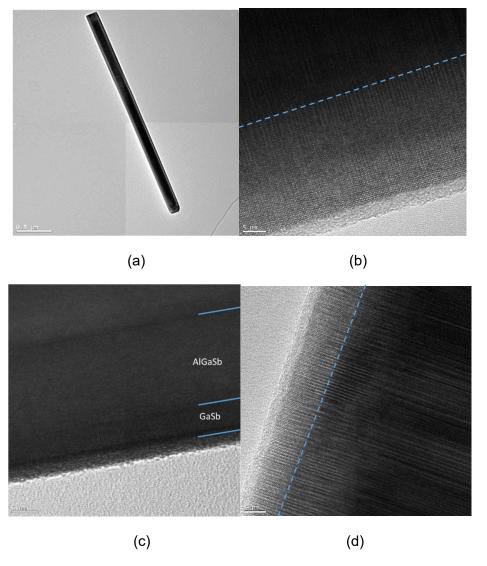

The EDX analysis can only show the elemental composition and distribution qualitatively. The precise thickness of shell cannot be determined. Therefore, high-resolution transmission electron microscopy (HRTEM) measurements are necessary. HRTEM allows direct imaging of the crystallographic structure down to Ångström level. The method is extensively used to analyze crystal structures of semiconductors at atomic scale.

To measure the shell thickness by HRTEM, the nanowires were again transferred on TEM grids. The TEM images were taken by aligning the nanowires to the <211> zone axis or <110> zone axis of the ZB structure. Under <110> zone axis, the contrast between core and shell as well as the crystal structure of core and shell can be distinguished, while under the <211> zone axis, only the contrast between core and shell can be observed [28]. Exemplarily, the Figure 2-11 (c) is taken from <211> zone axis. The contrast between core and shell can be easily observed. The images (b) and (d) are taken from <110> zone axis and both the contrast as well as the crystal structure can be seen. A large number of stacking faults in InAs nanowires can be seen and the defects penetrating from core to shell indicates the epitaxial growth of the Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb shell. The interface between InAs and Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb is smooth and abrupt, as shown in Figure 2-11 (a). The thin GaSb cap layer can only be observed in Figure 2-11 (c) with a thickness of around 5.75nm. The

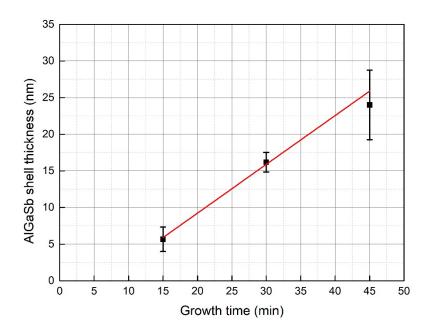

Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb shell growth time for Figure 2-11 (b), (c) and (d) are 45min, 30min and 15min, respectively. The thickness of the native oxide is 3-4nm for all TEM images. The relationship between Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb shell thickness and the corresponding growth time is shown in Figure 2-12. The Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb shell thickness is calculated by subtracting the thickness of GaSb shell (set as 5.75nm) from the total shell thickness. From Figure 2-12, a growth rate of 40nm/h for the Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb shell is obtained. This growth rate is based on the shell thicknesses of only 3-4 nanowires, the result needs to be further proven based on more nanowire data.

Figure 2-11. TEM images for InAs/Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb nanowires: (b) Nanowire with shell growth time 45min. a) and c) Nanowire with shell growth time 30min. d) Nanowire with shell growth time 15min.

Figure 2-12. Al<sub>0.6</sub>Ga<sub>0.4</sub>Sb shell thickness versus the corresponding growth time. The red line is the linear fit for the three different growth time.

### 2.3 Selective growth of InAs nanowires by MBE - new method

### 2.3.1 Growth mechanism

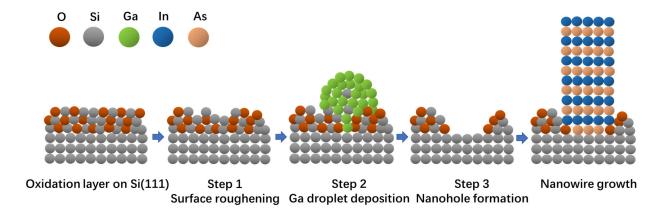

Considering the low reproducibility of the growth method introduced in section 2.1, a more stable method which is less sensitive to the substrate preparation is required. In pervious study [30], Ga pre-deposition technique has been tried for vapor-liquid-solid growth of InAs nanowires without patterning the substrate. Ga droplets create pinholes in the thin oxide which cover the Si (111) substrate as the start sites for the growth of InAs nanowires. However, the yield of InAs nanowires is low and a large amount of crystallites is achieved rather than nanowires. Recently, a high reproducible method to grow GaAs nanowires on native-SiO<sub>x</sub>/Si(111) by using Ga pre-deposition technique was demonstrated in [34][35]. A high yield of vertical nanowires can be obtained and therefore, the method is adopted as a reference in this study. for the vapor-solid growth of InAs nanowires on prepatterned Si substrate.

In this method, a thin oxide layer is created on the Si (111) substrate followed by a surface modification procedure (SMP) before InAs nanowire growth, which consists of 3 steps:

Step 1: Surface roughening at high temperature,

Step 2: Ga droplets are deposited on the thin  $SiO_x$  layer covering the Si (111) substrate. Ga can alloy with the Si from  $SiO_x$  above a certain temperature and create small openings in the underlying  $SiO_x$  layer,

Step 3: Ga droplets are then evaporated by thermal annealing and nano holes are left behind.

In the following growth process, the nucleation of the InAs nanowires take place in the holes. The schematic of the process is shown in Figure 2-13.

Figure 2-13. Schematic of the Ga assisted SMP of the Si(111) substrate for the InAs nanowire growth .

There are several advantages of this method, of which the highly reproducible growth results and the high yield of vertical nanowires-are the two most attractive. It should be mentioned that Ga instead of In droplets are used because the solubility of Si in liquid In is very low and the pinholes cannot be created, whereas the solubility of Si in liquid Ga is much higher [36].

In this study, the precondition of the Ga droplet assisted substrate SMP is to have a thin  $SiO_x$  layer at the bottom of the patterned holes. So, the substrate preparation process needs to be modified. The ex- situ standard substrate preparation process is shown in Figure 2-14 and is as following:

The steps a)-d) are similar as presented in section 2.1.1, except that after RIE process there is no dipping into the 1% HF solution. It should be mentioned that the RIE time is 110s.

In step e) the PMMA resist is removed using acetone (6min) and isopropanol (2min). Afterwards, 10 min oxygen plasma cleaning (300W, 200sccm) at Giga batch is performed.

Then, in step f), the sample is cleaned in Piranha solution (for 10min followed by 30s etching in1% HF solution. 30s is enough to get rid of residual SiO<sub>2</sub> inside the hole after RIE.

The last step g) before loading the sample into the MBE system is to dip it into  $37\%\ H_2O_2$  solution for 1min to re-oxidize the Si surface inside the holes. As studied in [37], the difference of the oxidation rates of hydrogen peroxide on Si (111) surface between the first and second bilayer is significant. The topmost bilayer is quickly oxidized by  $H_2O_2$  within 30min as well as the second bilayer cannot be totally oxidized after 2 months, so that obtaining a very thin oxide layer (below 1nm) is very easily controlled. Moreover, different durations between 30s-30min of the Si (111) oxidation using  $H_2O_2$  are investigated in [30] and 1min shows the highest density of grown InAs vertical nanowires. By using  $H_2O_2$  substrate re-oxidation for 1min, the desired thin silicon oxide inside the holes can be obtained.

Figure 2-14. The ex-situ substrate preparation for selective growth of InAs nanowires. After step (g), there is a thin oxidation layer in the holes.

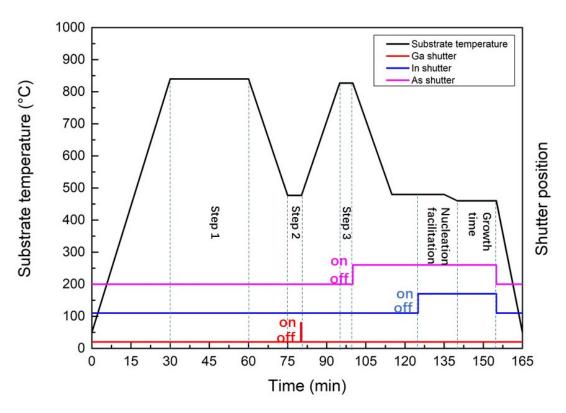

After ex-situ substrate preparation, the sample is loaded into the load lock chamber of MBE system and baked at 200°C for 45min. Then, an additional bake at 400°C for 1h is done in the preparation chamber. Finally, it is transferred into the MBE chamber for SMP and nanowire growth. The substrate temperature profile during SMP and the nanowire

growth, as well as the supplied fluxes n are shown in Figure 2-15. The SMP is conducted in the following sequence:

Figure 2-15. The substrate temperature profile and status of Ga/In/As fluxes during SMP and nanowire growth.

Step 1: Thermal annealing of the substrate to modify the thin SiO<sub>2</sub> surface inside the holes. High temperature is necessary to roughen the SiO<sub>2</sub> surface. This helps to have enough Ga atoms remaining on the substrate surface after Ga deposition, as discussed in [34].

Step 2: Lowering the substrate temperature to 477°C, keep it for 5 min to stabilize the temperature and then open Ga flux with growth rate 0.16 um/h for 17.6s (the beam flux is given in equivalent growth rate of planar GaAs layer). Ga droplets are formed on the substrate surface, mainly in the holes. Because the thickness of silicon dioxide outside the holes is approximately 14nm, Ga droplets does not big enough to penetrate through. So that the openings are created only inside the holes.

Step 3: Thermal annealing of the substrate at 827°C for 5 min to evaporate Ga droplets completely and enlarge the openings. The openings are the sites where nucleation of nanowire growth takes place. Most likely, the Ga droplets are evaporated totally during the thermal annealing procedure [38] and the InAs nanowires does not contain any Ga at the bottom.

After the surface modification process, the growth procedure is the same as in section 2.1.2.: The temperature of substrate is reduced to  $480^{\circ}$ C with As flux of  $4 \times 10^{-5}$  mbar for 10min, then the In shutter is opened with flux which corresponds to a growth rate of 0.08  $\mu$ m/h, while As flux remains at  $4 \times 10^{-5}$  mbar and the nanowire starts to grow for 10min. Then, the substrate temperature is reduced to  $460^{\circ}$ C in 5 min and simultaneously the In rate is reduced to  $0.03~\mu$ m/h and As BEP is reduced to  $2.5 \times 10^{-5}$  mbar. This growth conditions are maintained until the end of the growth and the corresponding time is defined as the growth time.

#### 2.3.2 Growth results and analysis

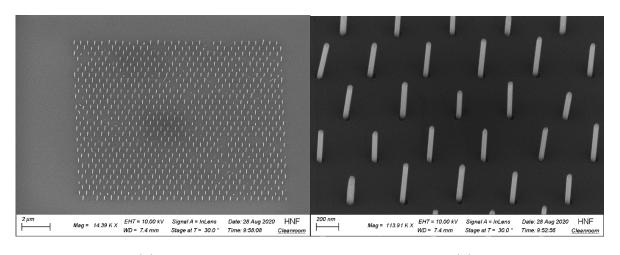

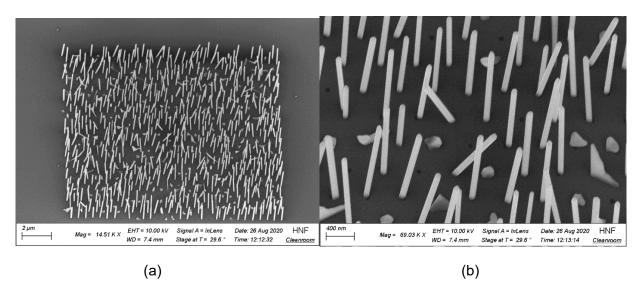

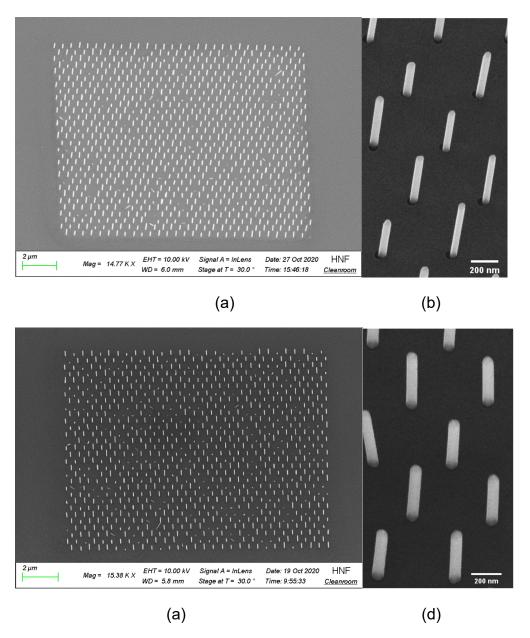

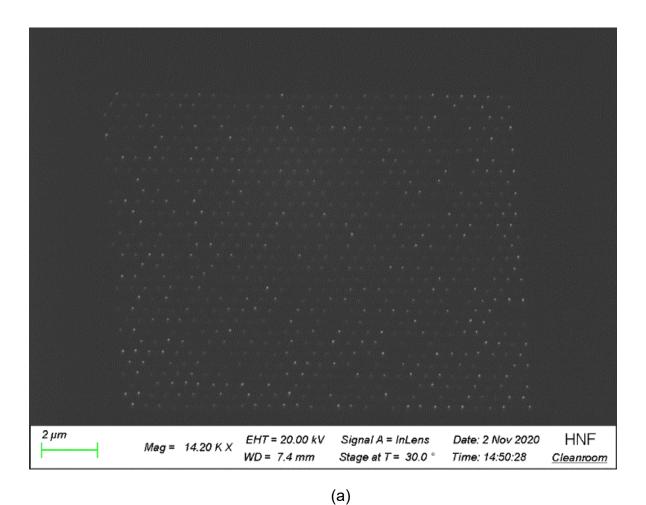

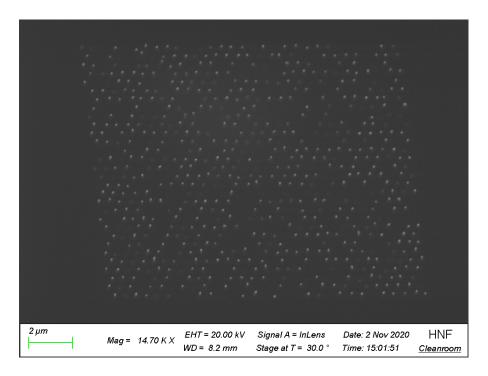

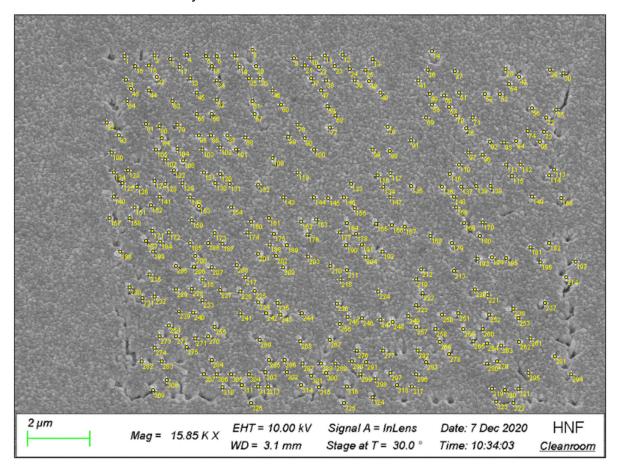

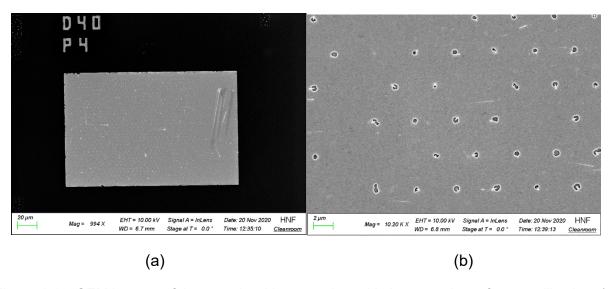

The growth result after the standard substrate preparation and growth process is shown in Figure 2-16. In the areas with hole diameter 20nm and 40nm, a very high density of vertical nanowires with very few crystallites or tilted nanowires is clearly observed.

(c) (d)

Figure 2-16 30° tilted SEM images from InAs nanowire arrays grown with new substrate preparation method: (a) Overview of a nanowire array in the area D40P500 with growth time 15min. (b) Close-up of several nanowires in (a). (c) Area D20P500 with growth time 30min. (d) Area D40P2 with growth time 1h.

#### 2.3.3 The influence of different substrate preparation processes

The nanowire growth presented in section 2.1 is very sensitive to substrate treatment. So, it is necessary to know how changes in the ex-situ substrate preparation influence the new nanowire growth method.

The growth results with 110s RIE process and 20s HF solution immersion, and the growth results with 130s RIE process and totally 120s HF solution immersion are shown in Figure 2-17. Both samples show similar growth results regarding the nanowire length, diameter and the yield. Thus, the HF immersion time can be reduced to 30s with no doubt. Based on the same experiments one can say that the growth is also not sensitive to the RIE time. We can conclude that the new substrate preparation method using Ga droplets gives more reliable and stable growth results than the method presented in section 2.1.

Figure 2-17. Comparison of different ex-situ substrate preparation. (a) substrate processed with 110s RIE etching and 20s HF dipping. (b) substrate processed with 130s RIE etching and 60s HF dipping directly after RIE process plus 60s HF solution dipping after cleaning with Piranha solution. Both images are with growth time 1h30min from area D20P500.

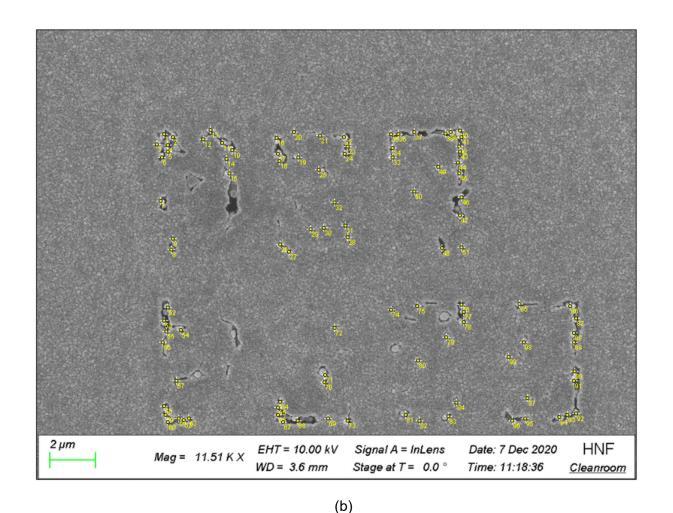

#### 2.3.4 The influence of different substrate re-oxidation before MBE growth

In the standard substrate preparation, 37% H<sub>2</sub>O<sub>2</sub> solution is used to re-oxidize the Si surface inside the holes. It is known that Si substrate can also be oxidized by storing in the air for certain time resulting in a thin layer of native oxide. As reported in [39], for Si(111) substrate at atmospheric humidity 40%, the thickness of native oxide remains at around 0.7nm-0.8nm for a storing time longer than 1 week. For comparison, one sample was stored in the air in the cleanroom for 1 week and afterwards, it was grown under the standard growth condition. The result is shown in Figure 2-18. It can be observed clearly that the growth result is worse than on the substrate with H<sub>2</sub>O<sub>2</sub> treatment as shown in Figure 2-17 (a) and (b). There are more empty holes, tilted nanowires and crystallites.

Figure 2-18 30° tilted SEM image of the nanowire array D40P500. The growth time is 1h30min and the substrate is re-oxidized in the air before loading into MBE (a) Overview of the nanowire array. (b) Close-up of several nanowires.

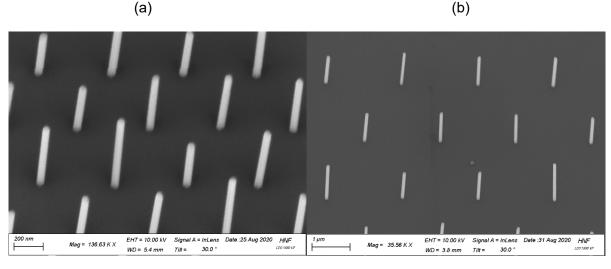

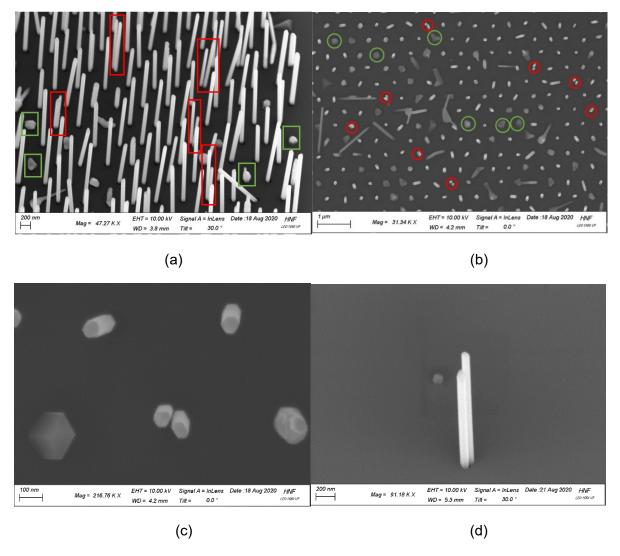

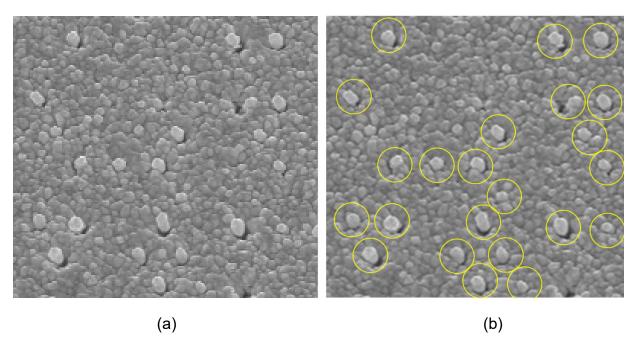

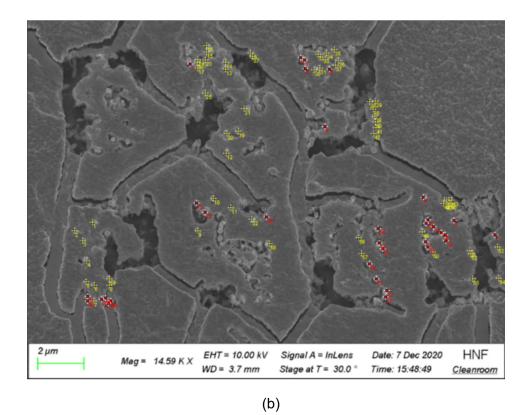

#### 2.3.5 The influence of different hole diameters

The images above are all from arrays with hole diameters 20nm or 40nm. Basically, from one hole only one nanowire grows. But for larger hole diameters 60nm and 80nm, two nanowires can grow from one hole, as shown in Figure 2-19. (a) and (b) shows the overview of nanowire array with D60P500. The twin nanowires are marked with red frames (circles) and the crystallites are marked with green frames (circles). Images (c) and (d) displays the twin nanowires with higher magnification. The nanowires have an irregular hexagonal morphology, as indicated in image (c).

Figure 2-19 (a) 30° tilted SEM image from the array D60P500 (b) Top view SEM image from the same array. (c) Top view of nanowires with higher magnification. (d) Close-up of twin nanowires.

Figure 2-20. The top view of SEM images from the arrays (a) D20P500 (b) D40P500 (c) D60P500 and (d) D80P500. The growth time of this sample is 1h30min. In image (d) it appears that even three nanowires can grow from one hole, as shown in the fourth hole position in the first line.

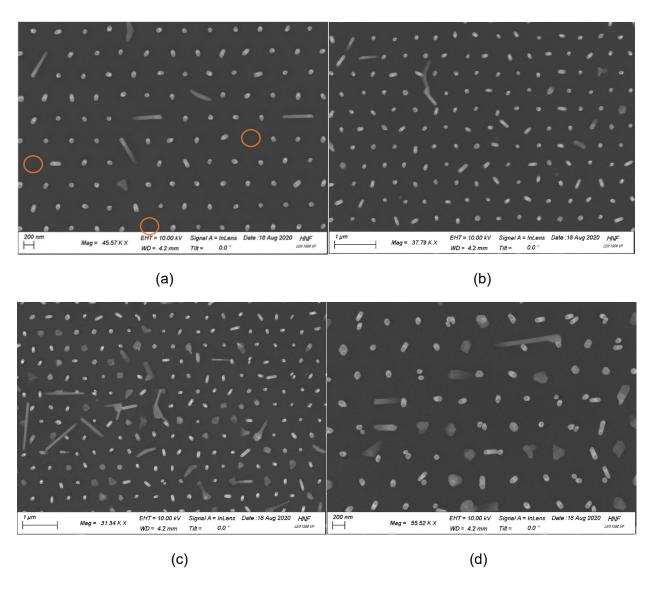

As displayed in Figure 2-20, the yield of vertical nanowires shows hole diameter dependence. With increasing hole diameter, the number of twin nanowires, tilted nanowires and crystallites increases. The yield of nanowires (defined as the ratio between normal single vertical nanowires and all the other structures) function of hole diameters is shown in black in the Figure 2-21. It is obviously that with increasing hole diameter, the yield decreases while the percent of twin nanowires and crystallites/inclined nanowires increases. The yield of nanowires in the array D20P500 is 94% while in the array D40P500 is 88%. It should be mentioned that when the diameter is 20nm, there are a few empty holes, as shown in orange circles in Figure 2-20 (a), which doesn't show up for

larger hole diameters. Overall, the arrays with hole diameters 20nm and 40nm have the best results. Therefore, the electrical measurements in chapter 5 are based on the arrays with hole diameters of 20nm and 40nm.

Figure 2-21. The relationship between hole diameters and the percent of normal single vertical NWs, twin nanowires, as well as tilted nanowires and crystallites.

The reason for the twin nanowires in one hole could be that holes with larger diameters provide a larger area to accept the depositing of more Ga droplets in the pre-deposition step. As reported in [34], the Ga droplets exhibit diameters in the range of 16-25nm and height in the range of 8-12nm, and the pinhole in the thin oxide layer under the vertical nanowires is approximately 5-8 nm in diameter. Therefore, for hole diameters 20nm and 40nm, only one droplet deposits inside the hole, but for hole diameters 60nm or 80nm, it is possible that two droplets (or even three droplets for 80nm) deposit inside the hole, react with the SiO<sub>x</sub> thin layer separately and create openings separately, which results in more than one nucleating sites inside the hole, therefore more than one nanowire can grow from one hole.

#### 2.3.6 The influence of growth time and different pitches

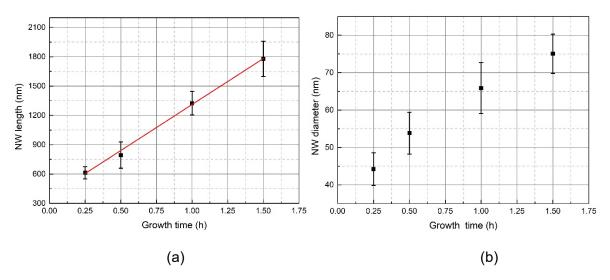

As shown in Figure 2-22 (a), with increasing growth time, the length of nanowires increases almost linearly. The equation of the fitting line is

The y-axis intercept indicates that the nanowires has already an average length of 371nm after the nucleation facilitation time. The growth rate is approximately 940 nm/h.

As plotted in Figure 2-22 (b), the nanowire diameter increases with time faster at the beginning and slightly slower later.

Figure 2-22. The relationship between nanowire length/diameter and growth time. These data are based on the measurement of 10 nanowires from array D40P500 from each sample. The errorbars represent the standard deviation of the ten measurements.

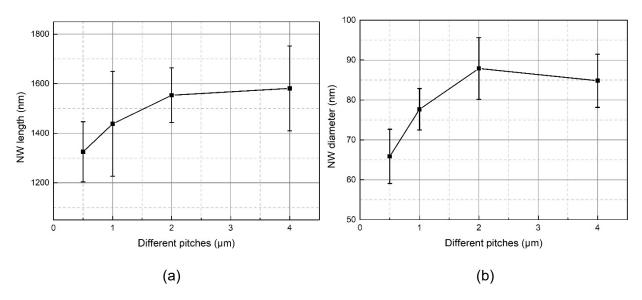

In Figure 2-23 the nanowire length and diameter are plotted function of the pitches. As seen, the nanowire length and the nanowire diameter increase with increasing pitches from 500 nm to 2  $\mu$ m, but for pitch 2  $\mu$ m and 4  $\mu$ m, the nanowire length keeps almost constant, the diameter can even decrease. This trend is the same as shown in [28]: below 2 $\mu$ m pitch the growth is in competitive growth regime, the growth rate increases as the capture area for surface diffusing In adatoms per nanowire increases. Above 2  $\mu$ m pitch, the growth is in diffusion limited regime, the pitch is larger than twice of the diffusion length of In adatoms and therefore the growth is limited by the diffusion length of In adatoms. The deviation amount of nanowire length and diameter is irregular with increasing pitches.

Figure 2-23. The relationship between nanowire length/diameter and pitches. These data are based on the measurement of 10 nanowires for each pitch from an array D40P500 with growth time 1h.

## 3. Passivation of InAs nanowire by ALD

In order to investigate the influence of the dielectric passivation on the electrical properties of the InAs nanowires, in-situ atomic layer deposition (ALD) is used to grow an  $Al_2O_3$  shell. In the ALD chamber, the reaction between the precursor trimethylaluminum (TMA,  $Al(CH_3)_3$ ) and the co-reactant  $H_2O$  occurs at 250°C. After 125 cycles around 10nm thick  $Al_2O_3$  shell is deposited on the InAs nanowires.

After the growth of InAs nanowires in the MBE chamber, the sample needs to be transferred to ALD chamber without taking it out from the ultrahigh vacuum. During the MBE growth, the substrate is upside down. On the contrary, the substrate is right side up during ALD growth. In this situation, a pocket wafer and flipping ring are needed in order to flip the substrate 180° before to be introduced in the ALD chamber. The flipping ring is thicker than the normal ring.

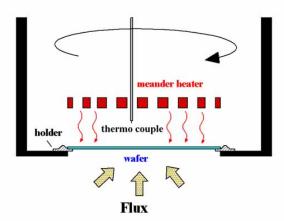

As mentioned in section 2.1.2, the substrate temperature in the MBE system is measured by a thermocouple. The thermocouple is situated closely above the sample, as shown in Figure 3-1. But due to the thermal obstruction of the pocket wafer between thermocouple and substrate and the different ring, the same temperature measured by the thermocouple correspond to a real temperature of the substrate different from the real temperature when using the normal ring.

Figure 3-1. Schematic of the substrate, substrate holder and substrate heater during growth. [40]

To set the substrate temperature during growth correctly, the real temperature of substrate during growth needs to be measured. The real temperature measurement is

based on emissivity corrected pyrometry. The pyrometer is located at the bottom of the chamber. It is a remote-sensing thermometer, which uses the amount of thermal radiation emitted from objects to determine their temperature. The emissivity can be corrected using the reflectance measured in the same time.

First, a sample was grown with the normal ring and the real temperature of the substrate during the whole growth process was recorded. The real temperature is usually lower than that measured by the thermocouple, as shown in Table 3-1. Afterwards, another substrate was grown with flipping ring and pocket wafer. During the growth, the same real substrate temperatures have been used and the new corresponding thermocouple temperatures have been recorded. The correspondence between the thermocouple temperature and the real temperature is shown also in Table 3-1. Figure 3-2 shows an array of Al<sub>2</sub>O<sub>3</sub> passivated nanowires using for the MBE growth the temperature calibration of the flipping ring. The nanowires are grown successfully, which indicates the correct growth temperature.

Table 3-1 The growth temperature calibration for normal and flipping ring

| Normal ring                   |                            | Flipping ring with pocket wafer |                            |  |

|-------------------------------|----------------------------|---------------------------------|----------------------------|--|

| T <sub>thermocouple</sub> /°C | T <sub>pyrometer</sub> /°C | T <sub>thermocouple</sub> /°C   | T <sub>pyrometer</sub> /°C |  |

| 840                           | 760                        | 985                             | 760                        |  |

| 477                           | 455                        | 574                             | 455                        |  |

| 827                           | 750                        | 975                             | 750                        |  |

| 480                           | 458                        | 578                             | 458                        |  |

| 460                           | 425                        | 558                             | 425                        |  |

Figure 3-2. The morphology of  $Al_2O_3$  passivated InAs nanowires grown with the flipping ring with nanowire growth time 15min and 10nm  $Al_2O_3$  passivation (array D20P500).

## 4. InAs nanowire-array based device fabrication

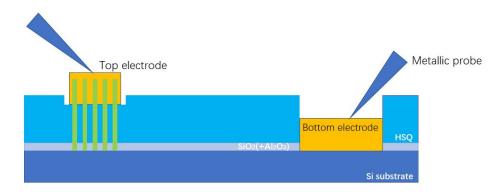

The usual pick and place approach for nanowire device fabrication which involves only one single nanowire is very time consuming, and needs high requirements for the lithography. Therefore, InAs nanowire-array based devices are fabricated in this thesis, in order to measure the electrical characteristics of nanowires and to investigate the influence of passivation.

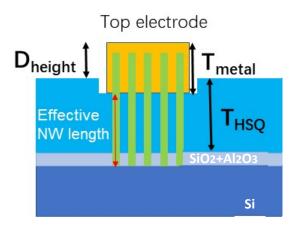

The schematic of the device architecture is shown in Figure 4-1. Each nanowire array as a whole is connected by a top electrode and the bottom electrode is directly deposited on the highly n-doped Si substrate. The electrical characteristic can be achieved by connecting metallic probes on top and bottom electrodes. To achieve this device architecture, the following 4 steps are performed. The detailed description is shown afterwards.

- 1. Dicing of the 2.5\*2.5 cm<sup>2</sup> substrate

- 2. Planarization the samples with HSQ

- 3. Revealing the top of nanowires

- 4. Top/bottom electrode fabrication

Figure 4-1. The schematic of the device architecture.

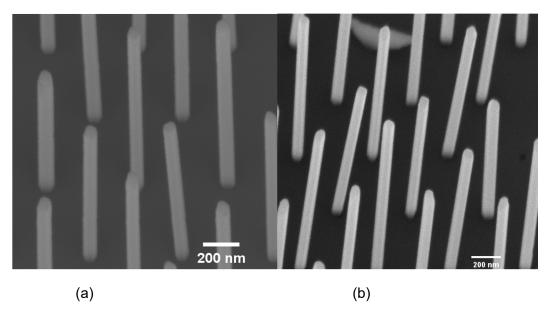

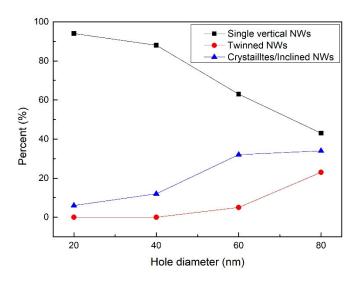

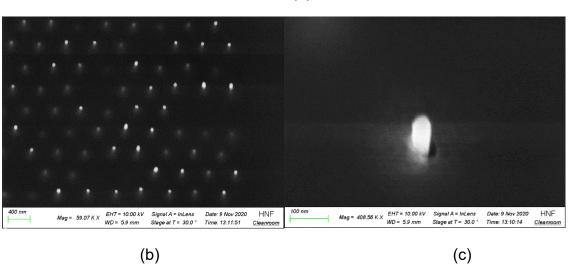

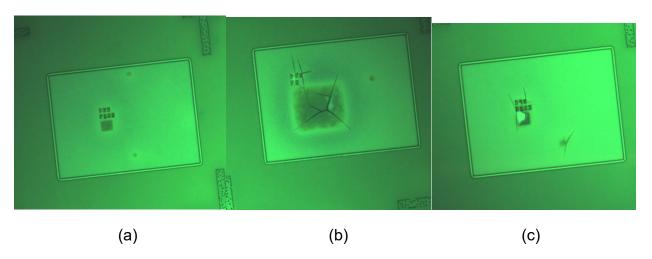

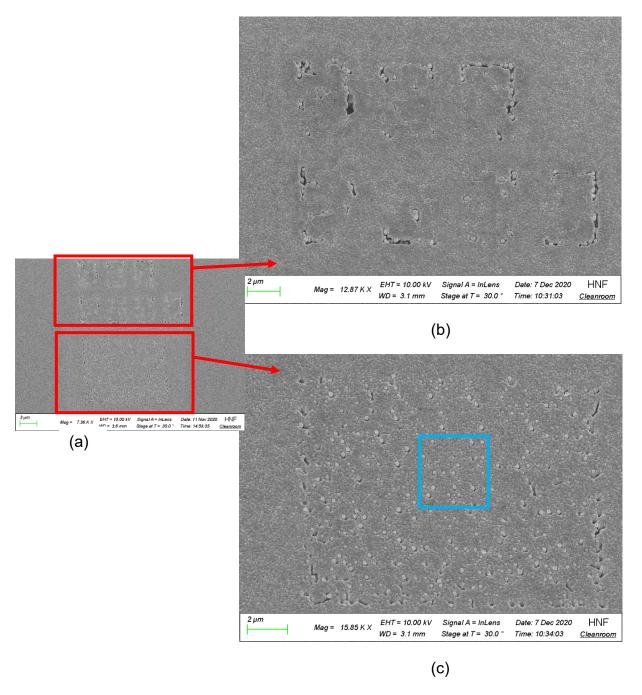

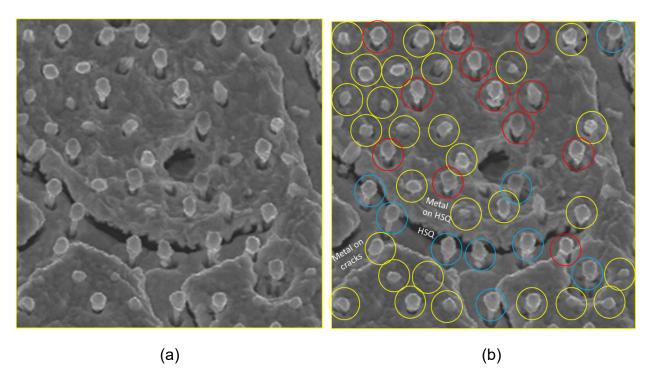

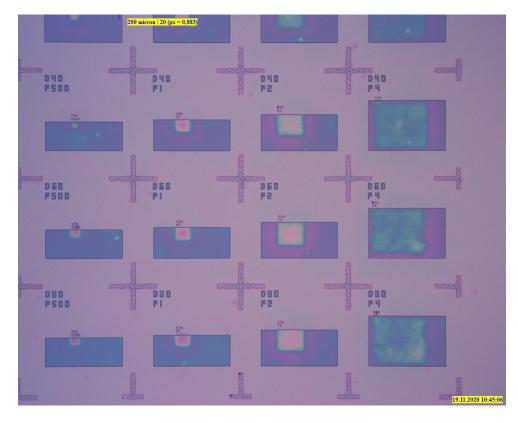

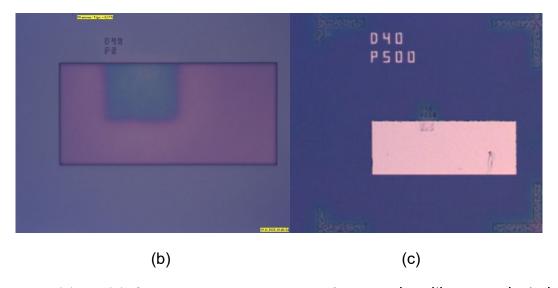

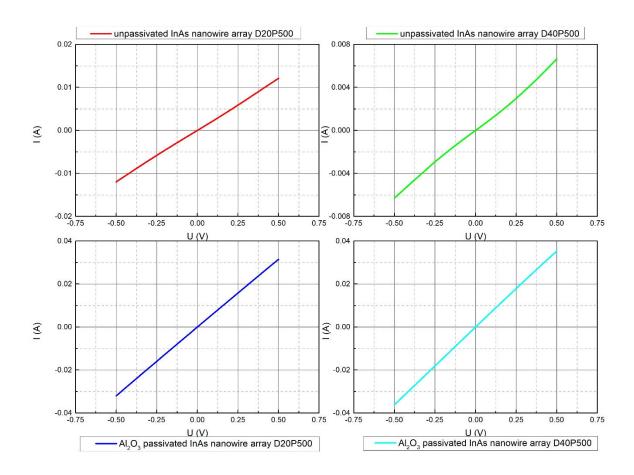

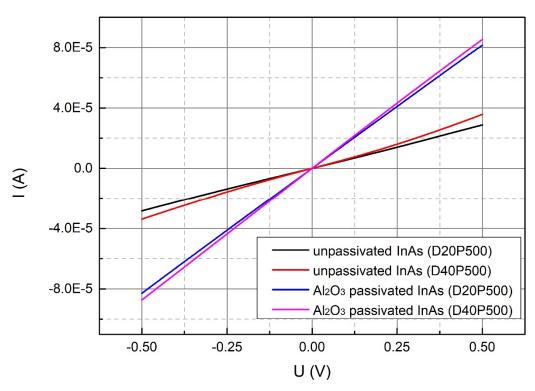

The fabrication is done using a sample with InAs nanowires and one with  $Al_2O_3$  passivated InAs nanowires. They are both with 15min nanowire growth time and the thickness of the  $Al_2O_3$  shell for passivated nanowires is around 10nm. Exemplarily, SEM images of a nanowire array from both samples are shown in Figure 4-2. Comparing (b) and (d), it is obviously that the diameter of the nanowires in (d) is larger than in (b), which indicates the presence of  $Al_2O_3$  shell.

Figure 4-2. SEM micrographs of the samples used for the device fabrication. (a) and (b) Nanowire morphology of the array D40P500from the sample with InAs nanowires. (c) and (d) Nanowire morphology of the array D40P500 from the sample with Al<sub>2</sub>O<sub>3</sub> passivated InAs nanowires.

## 4.1 Dicing

First, after the growth, the 2.5\*2.5 cm<sup>2</sup> substrates was spin-coated with resist AZ5214E at 500rpm for 30s which was baked at 90°C for 3min. Afterwards, they were diced into 4 pieces each with the size 1.25×1.25cm<sup>2</sup>. The spin-coating speed was low because the nanowires are fragile and at high speed there is the risk to brake or bend. After dicing,

the substrates were cleaned with acetone and isopropanol without using ultrasonic bath because even 1 min in the bath at the lowest power will lead to the break of most of the vertical nanowires from the Si substrate. The processes mentioned bellow were all performed on these pieces with sample size 1.25x1.25cm<sup>2</sup>.

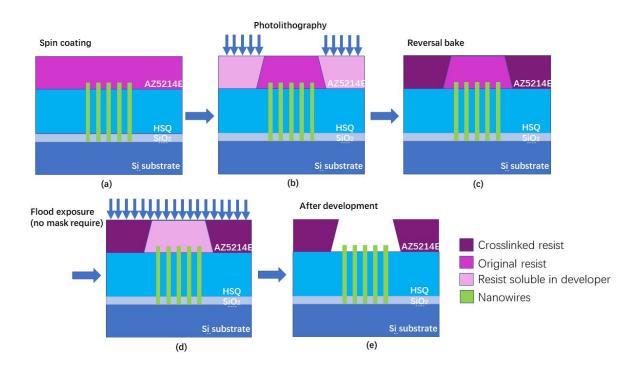

#### 4.2 Planarization with HSQ

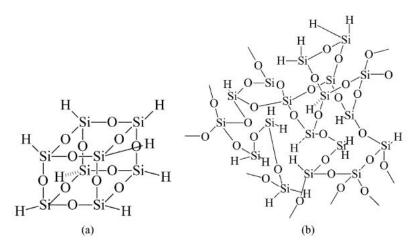

Prior to the fabrication of the top and bottom contacts, it is necessary to planarize the substrate surface. The polymer hydrogen silsesquioxane (HSQ) is used in this study as the planarization material. HSQ exhibits a good gap fill capability and low dielectric constant (k <3.0). Therefore, it is a potential candidate for the formation of interlayer dielectrics to enhance the performance of integrated circuits. HSQ is commercially available in a carrier solvent of methyl isobutyl ketone (MIBK). The fluidity of HSQ makes the spin-coating process possible and the layer can serve as an isolating and supporting material between top and bottom electrode. It can also work as negative inorganic electron beam resist with high resolution [41].

HSQ polymers consist of three-dimensional molecules with chemical composition (HSiO<sub>3/2</sub>)<sub>n</sub>. A representative molecular structure is illustrated in Figure 4-3 (a). HSQ has a mixed cage-network structure before curing and transforms from cage-network structure to network structure after curing, as seen in Figure 4-3 (b). During curing process, Si-H bonds disassociate, molecules rearrange and O-Si-O bonds form [42][43]. then HSQ turns into a material with similar chemical composition as SiO<sub>2</sub>.

Figure 4-3. (a) Cage structure of HSQ. (b) Network structure of HSQ. Taken from [44].

In the spin-coating process, the entire sample surface was covered with the HSQ solution and was left to stand for 2 min to ensure the filling of the narrow gap between the

nanowires. Afterwards, it was spun at 1000 rpm for 1 min (acceleration 200 rpm/s), and then baked on the hot plate at 150°C for 2min and at 220°C for 5min in order to remove the solvent and initiate structural changes. Then the sample was transferred into rapid thermal processing (RTP) equipment to cure the HSQ layer at 300°C for 15min in N<sub>2</sub> atmosphere. After this process, the HSQ structure was modified into an amorphous silica structure.

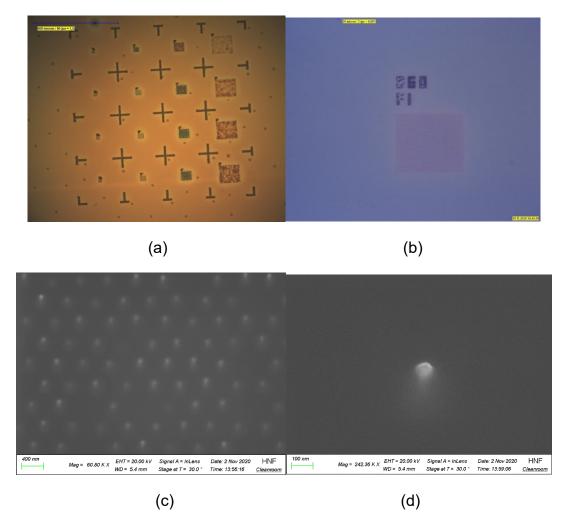

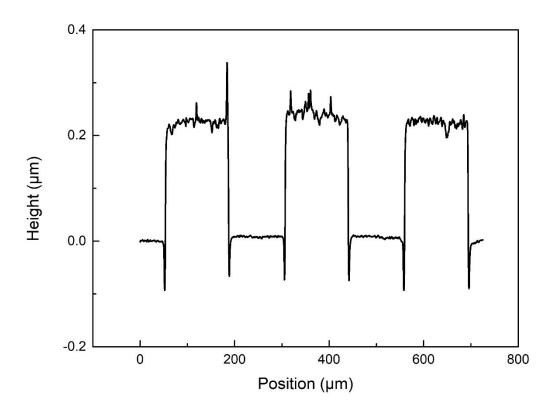

The thickness of HSQ was measured by Ellipsometer SE800. The thickness of one layer of HSQ under the above condition is 200±10 nm. The length of InAs nanowires with growth time 15min is around 600 nm. As a result, three layers of HSQ are required to planarize the nanowires. The spin-coating and RTP processes were repeated three times and around 600nm of dielectric layer was achieved after planarization.

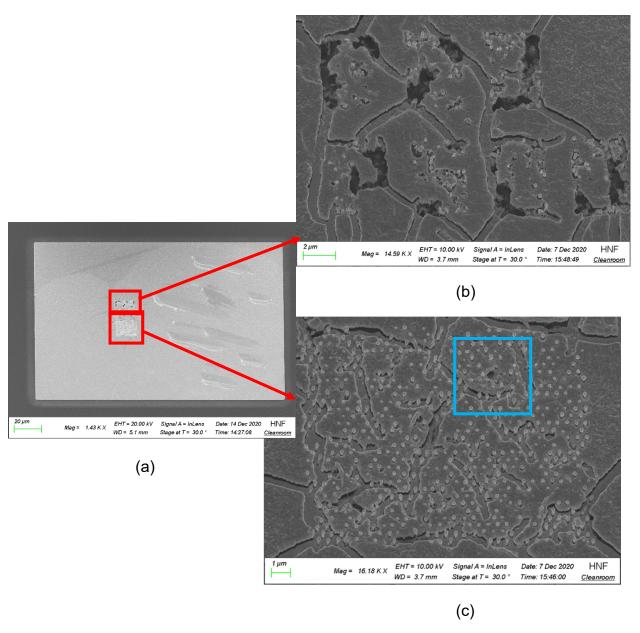

The Figure 4-4 shows images during the planarization of nanowires without passivation. Figure 4-4 (c) shows the most of the nanowires are totally covered by HSQ. For sample with  $Al_2O_3$  passivation, similar results were obtained.

Figure 4-4. Optical microscope (a) and (b) and SEM (c) and (d) images from the sample with InAs nanowires without  $Al_2O_3$  passivation. (a) After 1 layer of HSQ spin-coating. (b) After 3 layers of HSQ planarization. (b) Array D40P500 after 3 layers of HSQ planarization. (d) Close-up of a nanowire top.

### 4.3 Revealing the top of nanowires

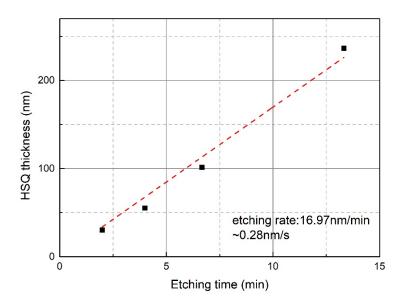

After the planarization process, the next step is to etch back the HSQ layer using RIE by CHF<sub>3</sub> in order to reveal the top of nanowires. The etching rate of HSQ in the RIE process using CHF<sub>3</sub> is around 0.28nm/s, as shown in Figure 4-5. 5min RIE is performed for both samples with and without passivation. After the RIE process, around 84nm HSQ is etched. Exemplarily, SEM images of both unpassivated and passivated nanowire areas are shown in Figure 4-6 and Figure 4-7, respectively.

Figure 4-5. The etching rate of HSQ in RIE process.

Figure 4-6. SEM images from the sample with unpassivated InAs nanowires after 5min RIE process (array D40P500). (a) Overview of the nanowire area. (b) and (c) Close-ups of the nanowire area.

(a)

(b)

Figure 4-7. SEM images from the sample with  $Al_2O_3$  passivated InAs nanowires after 5min RIE process (array D40P500) (a) Overview of the nanowire area. (b) close-up of the nanowire area.

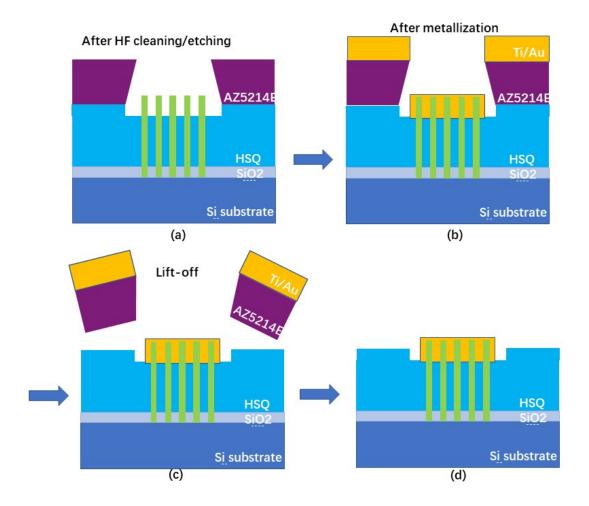

### 4.4 Top/bottom electrode fabrication

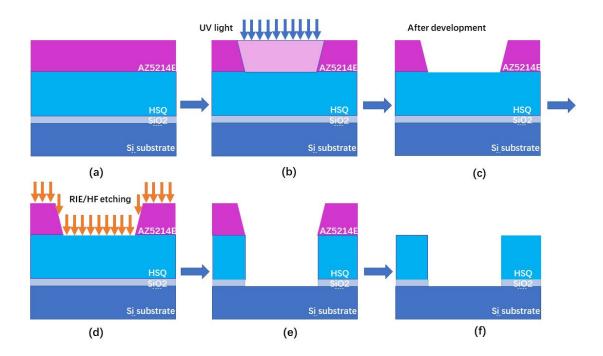

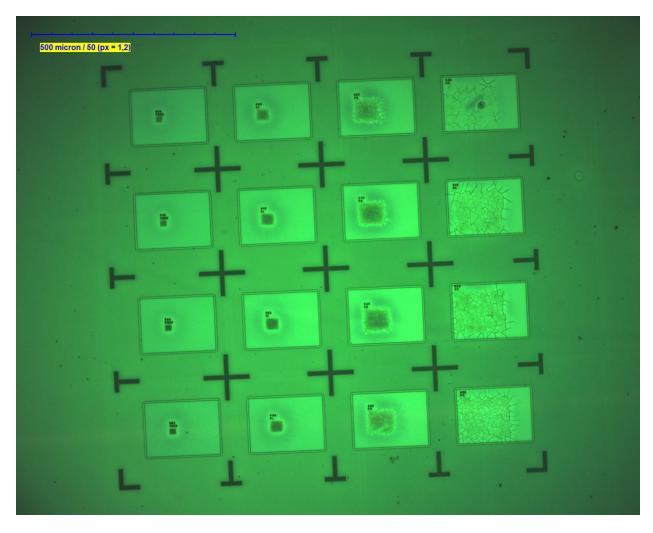

After exposing the top of nanowires, two photolithography processes are required. The first photolithography is used to open the Si substrate surface for the bottom electrodes. The AutoCAD pattern is shown in Figure 4-8(a). The HSQ in the two rectangles needs to be etched away until the surface of the Si substrate is reached. The second photolithography is to create the resist patterns for metal deposition of the top/bottom electrodes. The AutoCAD design is shown in Figure 4-7 (b) and (c). The metal stack for the top and bottom electrodes is deposited in one process. Close-up of one of the top electrodes is shown in Figure 4-8 (d), the top electrode has a rectangular shape and covers the nanowire array inside. The photoresist AZ5214E is used in both cases, as positive resist for etching and image reversal resist for metal deposition.

Figure 4-8. (a) AutoCAD patterns for the first photolithography (sample C). (b) AutoCAD pattern for second photolithography. The upper 4x5 fields are identical and investigated in this thesis. (c) Close-up of the field shown in the yellow square; it contains 4x4 rectangles, each rectangle corresponding to a nanowire array in Figure 2-1 (b) and to a top electrode after the metallization. (c) Close-up of one of the rectangles (array D20P500).

#### 4.4.1 First photolithography

In the first photolithography, the resist AZ5214E was used as positive photoresist, as shown in Figure 4-9 (a)(b) and (c). the detailed process is:

- (a) spin-coating of resist AZ5214E with 4000 rpm for 1min and acceleration at 500 rpm/s; then, soft bake at 95°C for 60 s; around 1.4 µm thick resist on the substrate is obtained.

- (b) transfer to Maskless Aligner MLA100 and expose with the dose 250 mJ/cm<sup>2</sup>.

- (c) development in developer AZ326 MIF for 1min.

Figure 4-9. Schematic of the first photolithography and RIE processes. This schematic is for sample with unpassivated InAs nanowires For the sample with  $Al_2O_3$  passivated InAs nanowires, there is an  $Al_2O_3$  layer of around 10nm thickness between  $SiO_2$  and HSQ.

During the exposure process, the photoactive compound in the exposed resist area will absorb the incoming ultraviolet light and the light will be attenuated along the path and

the effective exposed area shows a positive slope in depth, as shown in Figure 4-8 (b). As a result, the dissolution rate during development is higher at the top and lower at bottom resulting in a resist with positive slope, as shown in Figure 4-8 (c).

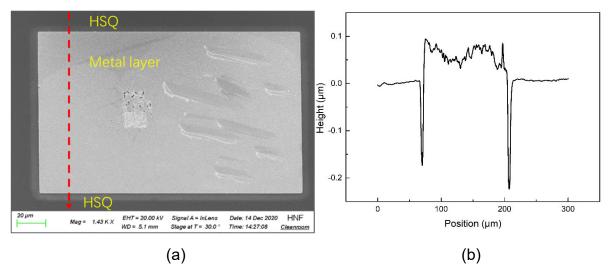

In this thesis, Maskless Aligner-MLA100 was used for the photolithography process. Making a real photomask necessary for the classical mask aligner is time consuming and the pattern cannot be changed once the mask has been fabricated. In comparison, the equipment MLA100 doesn't need a real photomask: the system takes the design file and writes the pattern on the resist-covered substrate with the help of a spatial light modulator. The design file can be redesigned conveniently and the writing time is within minutes, e. g. for the 12.5x12.5mm² substrate in this study, the writing process was finished within 5 min. The minimum feature size is 1µm, which is smaller than the minimum structure size of the AutoCAD patterns in Figure 4-7 (a) and (b). The power of the LED light source is 10W at 365nm.